# アナログ電子回路

授業開始までしばらくお待ちください。

# 授業の受講に関して

- 講義資料（スライド等）は Google drive に置く。授業前には虫喰い状態のスライドのみを提供するが、授業後に穴埋め版を uncovered フォルダに置くので復習に活用されたい。

<https://drive.google.com/drive/folders/1yzIsRZsVGFErhnfzn8Hycsn6nRPNCczn>

- 授業の録画も同じところに置く。

- ミニレポートは **Google Forms**

(<https://forms.gle/MpUmErDi6qk8GSUC6>) に提出。

# 授業の進め方

- 出席は UNIPA で取るが、出席そのものは評価せず。極論するとテストのみ出席で他は全欠席でも A 評価はあり得る。なお、**不正出席をした場合は 21 点の減点**とする。

- 基本的には**中間演習と期末試験**で評価。

- 毎回ミニレポートを課す。出す者は提出期間を厳守すること。

- 試験の不合格者は**毎回のミニレポートと出席**で少し救済する。

(しっかりした内容のミニレポートを概ね 9 割以上提出し、かつ UNIPA で 8 割以上遅刻せず出席していた場合最大 10 点程度の救済。提出数や出席数が少ない場合は救済幅が縮小する。いずれかが 7 割を下回ったら一切救済しない。締め切り後の提出は認めない。)

- スライド穴埋め版はその回の授業終了後に公開。

- 授業中に**スライドの誤りを見つけて指摘してくれた者には、誤り一箇所につき先着一名様限り 100 点満点 1 点相当の加点を行う。(ただしごく軽微なものなど、内容によっては加点しない場合もあり。)

2025

# S科アナログ電子回路

Analog Electronics

## 『ソース接地回路』

小林裕之

大阪工業大学 RD 学部システムデザイン工学科

OSAKA INSTITUTE OF TECHNOLOGY

6 of 14

a L<sup>A</sup>T<sub>E</sub>X + Beamer slideshow

## 基本的な考え方・方針

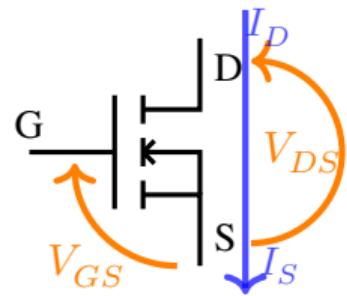

- 回路を**大信号 (DC)**と**小信号 (AC)**に分ける。

- 大信号では、**増幅の準備**（バイアス設計・**DC 解析**）を行う。

- MOS トランジスタなら \_\_\_\_\_ になるように

$V_{DS} > V_{GS} - V_T > 0$ 、

- バイポーラトランジスタなら BE 間を   方向  バイアスに、

CB 間を   方向  バイアスにする。さらに必要であれば  $I_E$  を求め \_\_\_\_\_ も求める。

- 小信号では、**信号増幅**自体の設計や解析 (**AC 解析**) を行う。

## 基本的な考え方・方針

- 回路を**大信号 (DC)**と**小信号 (AC)**に分ける。

- 大信号では、**増幅の準備**（バイアス設計・**DC 解析**）を行う。

- MOS トランジスタなら 飽和領域 になるように

$V_{DS} > V_{GS} - V_T > 0$ 、

- バイポーラトランジスタなら BE 間を 方向 バイアスに、

CB 間を 方向 バイアスにする。さらに必要であれば  $I_E$  を求め \_\_\_\_\_ も求める。

- 小信号では、**信号増幅**自体の設計や解析 (**AC 解析**) を行う。

## 基本的な考え方・方針

- 回路を**大信号 (DC)**と**小信号 (AC)**に分ける。

- 大信号では、**増幅の準備**（バイアス設計・**DC 解析**）を行う。

- MOS トランジスタなら 飽和領域 になるように

$V_{DS} > V_{GS} - V_T > 0$ 、

- バイポーラトランジスタなら BE 間を 順方向 バイアスに、

CB 間を 方向 バイアスにする。さらに必要であれば  $I_E$  を求め \_\_\_\_\_ も求める。

- 小信号では、**信号増幅**自体の設計や解析 (**AC 解析**) を行う。

## 基本的な考え方・方針

- 回路を**大信号 (DC)**と**小信号 (AC)**に分ける。

- 大信号では、**増幅の準備**（バイアス設計・**DC 解析**）を行う。

- ▶ MOS トランジスタなら 飽和領域 になるように

$V_{DS} > V_{GS} - V_T > 0$ 、

- ▶ バイポーラトランジスタなら BE 間を 順方向 バイアスに、

CB 間を 逆方向 バイアスにする。さらに必要であれば  $I_E$  を求め \_\_\_\_\_ も求める。

- 小信号では、**信号増幅**自体の設計や解析 (**AC 解析**) を行う。

## 基本的な考え方・方針

- 回路を**大信号 (DC)**と**小信号 (AC)**に分ける。

- 大信号では、**増幅の準備**（バイアス設計・**DC 解析**）を行う。

- ▶ MOS トランジスタなら 飽和領域 になるように

$V_{DS} > V_{GS} - V_T > 0$ 、

- ▶ バイポーラトランジスタなら BE 間を 順方向 バイアスに、

CB 間を 逆方向 バイアスにする。さらに必要であれば  $I_E$  を求め  $g_m \simeq \frac{qI_E}{kT}$  も求める。

- 小信号では、**信号増幅**自体の設計や解析 (**AC 解析**) を行う。

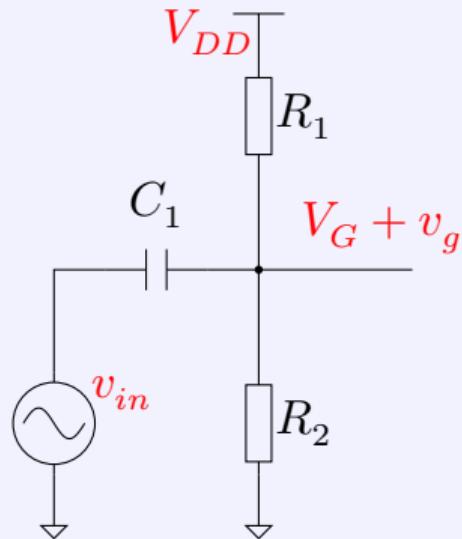

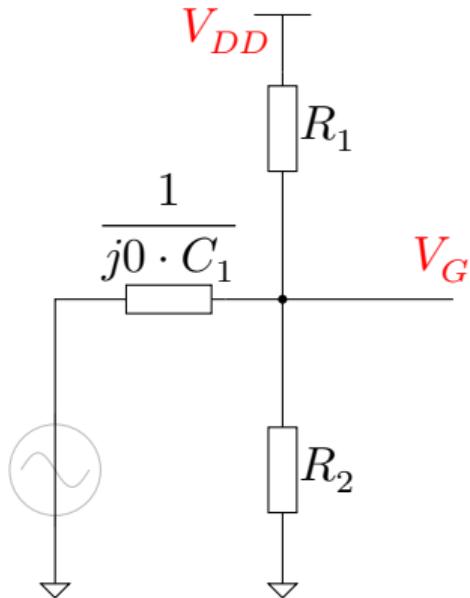

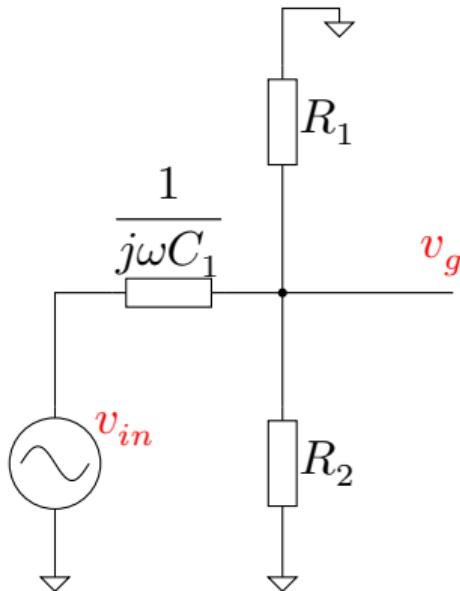

以下の『よくある入力部分の回路』における  $V_G + v_g$  を求めよ。

以下の『よくある入力部分の回路』における  $V_G + v_g$  を求めよ。

# バイアス + 信号を重ねの理で考える。

以下の『よくある入力部分の回路』における  $V_G + v_g$  を求めよ。

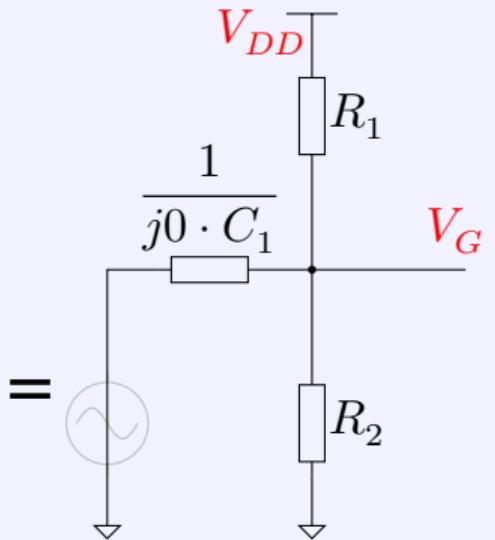

# DC 部分

- AC 信号はゼロとするので  $v_{in}$  のところは短絡 (0 V)。

- キャパシタは DC ( $\omega = 0$ ) に対して無限大  $\Omega$  のインピーダンス。

…ということから、↓ こうなる。

$$V_G =$$

# DC 部分

- AC 信号はゼロとするので  $v_{in}$  のところは短絡 (0 V)。

- キャパシタは DC ( $\omega = 0$ ) に対して無限大  $\Omega$  のインピーダンス。

…ということから、↓ こうなる。

$$V_G = \frac{R_2}{R_1 + R_2} V_{DD}$$

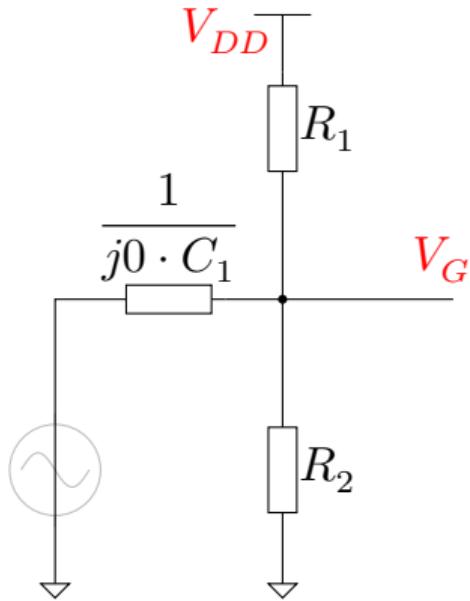

- DC 信号はゼロとするので  $V_{DD}$  は GND。

- キャパシタは  $1/j\omega C_1 \Omega$  のインピーダンス。

- …ということから、↓こうなる。

$$v_g =$$

=

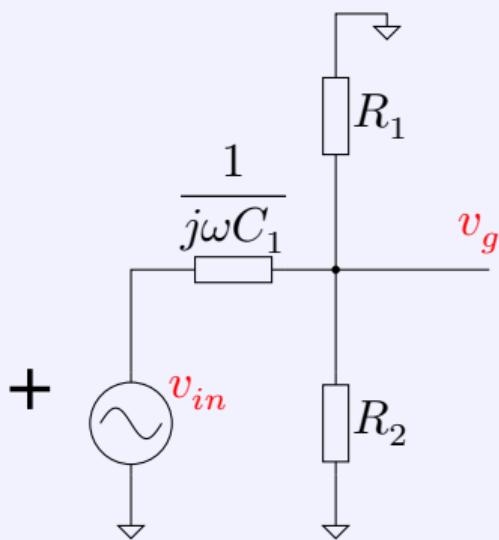

# AC 部分

- DC 信号はゼロとするので  $V_{DD}$  は GND。

- キャパシタは  $1/j\omega C_1 \Omega$  のインピーダンス。

- …ということから、↓こうなる。

$$v_g = \frac{R_1 // R_2}{\frac{1}{j\omega C_1} + R_1 // R_2} v_{in}$$

=

- DC 信号はゼロとするので  $V_{DD}$  は GND。

- キャパシタは  $1/j\omega C_1 \Omega$  のインピーダンス。

- …ということから、↓こうなる。

$$\begin{aligned}

v_g &= \frac{R_1 // R_2}{\frac{1}{j\omega C_1} + R_1 // R_2} v_{in} \\

&= \frac{j\omega C_1 R_1 R_2}{R_1 + R_2 + j\omega C_1 R_1 R_2} v_{in}

\end{aligned}$$

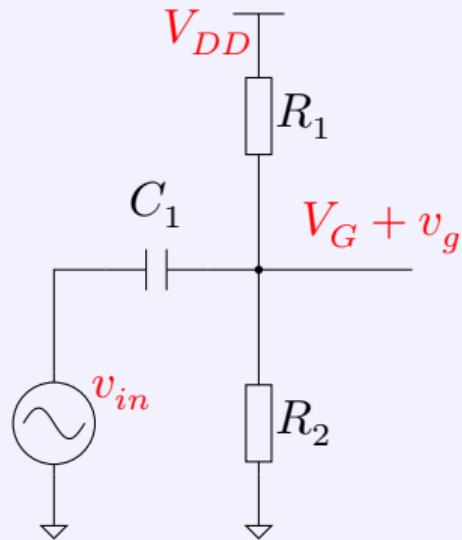

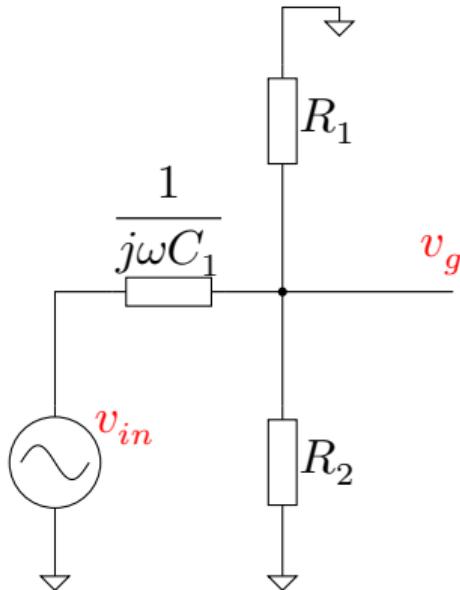

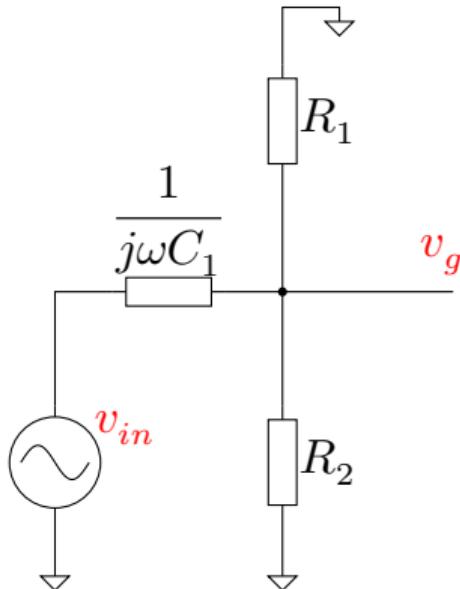

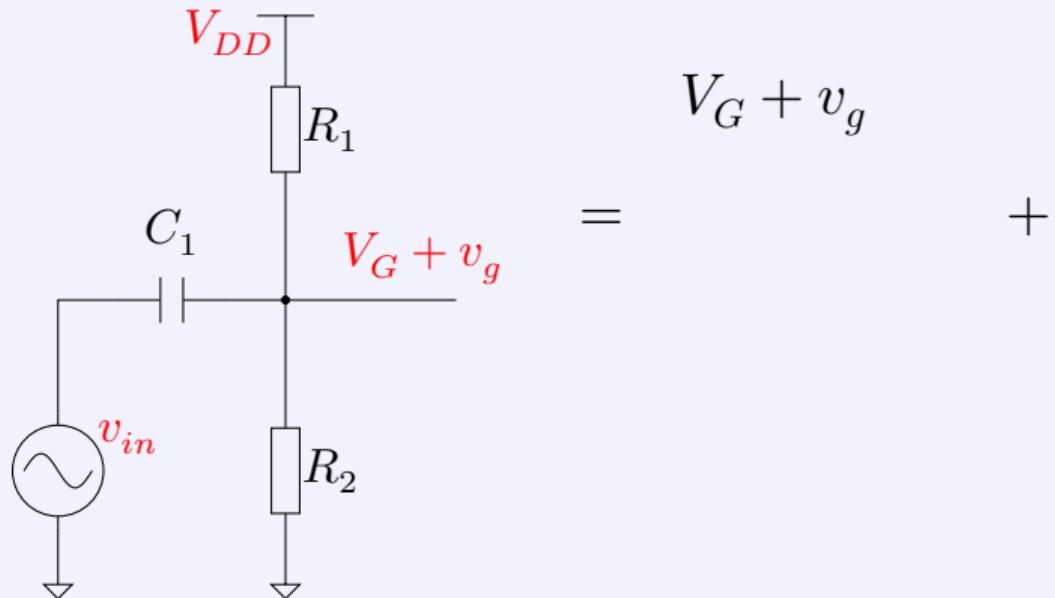

# バイアス + 信号を重ねの理で考える

以下の『よくある入力部分の回路』における  $V_G + v_g$  を求めよ。

# バイアス + 信号を重ねの理で考える

以下の『よくある入力部分の回路』における  $V_G + v_g$  を求めよ。

The circuit diagram shows a voltage-controlled voltage source (VCCS) with bias and signal inputs. A DC voltage source  $V_{DD}$  is connected to the top node. A resistor  $R_1$  is connected between the top node and the output node. A capacitor  $\frac{1}{j\omega \cdot C_1}$  is connected between the output node and ground. A resistor  $R_2$  is connected between the output node and the bottom node. A sinusoidal voltage source is connected between the bottom node and ground. The output voltage  $V_G$  is measured across the resistor  $R_2$ . The equation for the output voltage is:

$$V_G + v_g = \frac{R_2}{R_1 + R_2} V_{DD} +$$

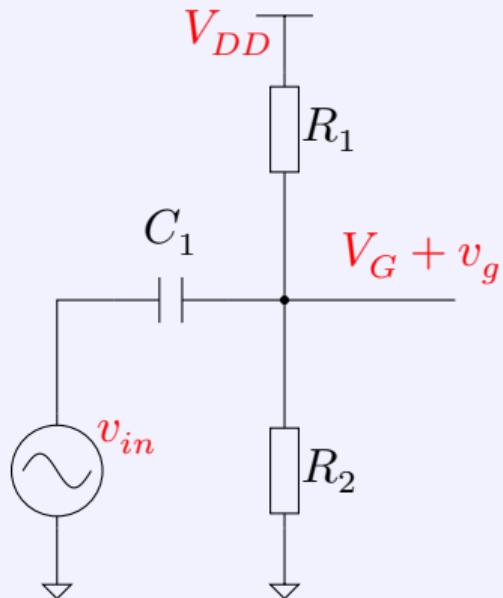

# バイアス + 信号を重ねの理で考える

以下の『よくある入力部分の回路』における  $V_G + v_g$  を求めよ。

The circuit diagram shows a voltage-controlled voltage source (VCCS) with a feedback path. A sinusoidal voltage source  $v_{in}$  is connected to the non-inverting input node. This node is also connected to the inverting input node through a resistor  $\frac{1}{j\omega C_1}$ . The inverting input node is grounded. The output node is connected to the inverting input node through a resistor  $R_1$ , and to ground through a resistor  $R_2$ . The voltage at the output node is labeled  $V_G + v_g$ . The circuit is set up to solve for this voltage.

$$V_G + v_g = \frac{j\omega C_1 R_1 R_2}{R_1 + R_2 + j\omega C_1 R_1 R_2} v_{in}$$

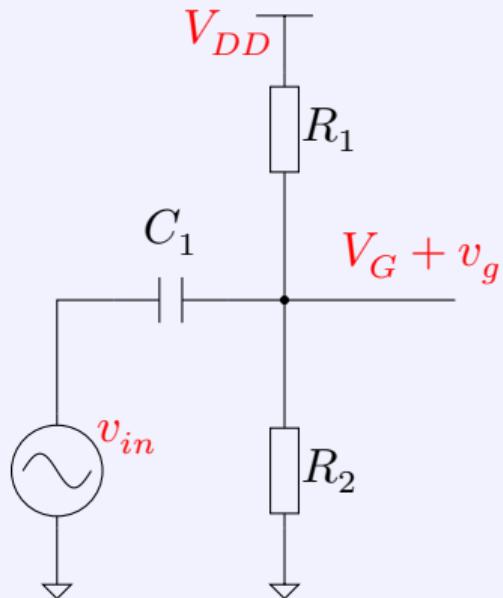

# バイアス + 信号を重ねの理で考える

以下の『よくある入力部分の回路』における  $V_G + v_g$  を求めよ。

$$\begin{aligned} V_G + v_g &= \frac{R_2}{R_1 + R_2} V_{DD} + \frac{j\omega C_1 R_1 R_2}{R_1 + R_2 + j\omega C_1 R_1 R_2} v_{in} \\ (\omega \rightarrow \text{大のとき}) \\ &= \end{aligned}$$

# バイアス + 信号を重ねの理で考える

以下の『よくある入力部分の回路』における  $V_G + v_g$  を求めよ。

$$\begin{aligned}V_G + v_g &= \frac{R_2}{R_1 + R_2} V_{DD} + \frac{j\omega C_1 R_1 R_2}{R_1 + R_2 + j\omega C_1 R_1 R_2} v_{in} \\&\quad (\omega \rightarrow \text{大のとき}) \\&= \underbrace{\frac{R_2}{R_1 + R_2} V_{DD}}_{\text{大信号}(V_G)} + \underbrace{v_{in}}_{\text{小信号}(v_g)}\end{aligned}$$

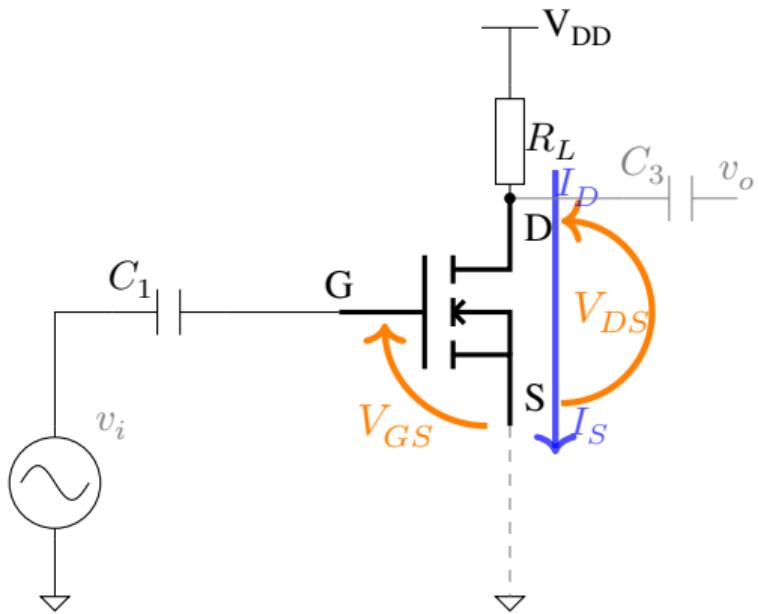

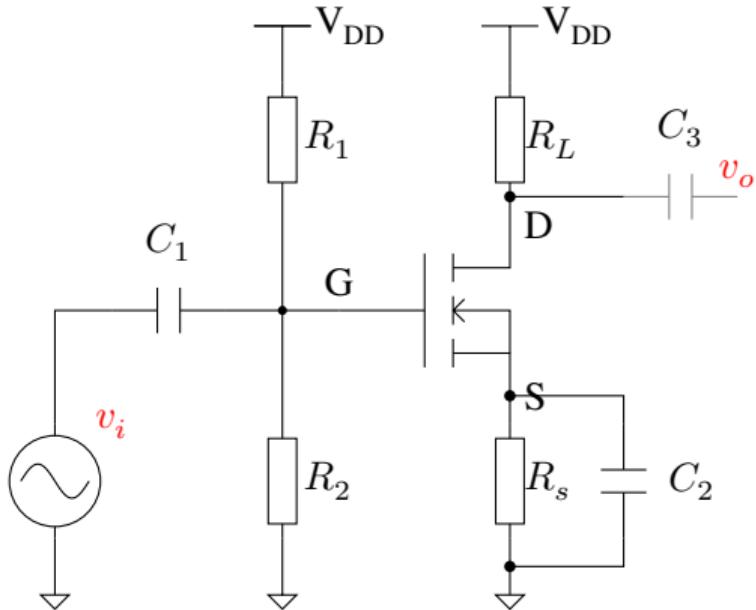

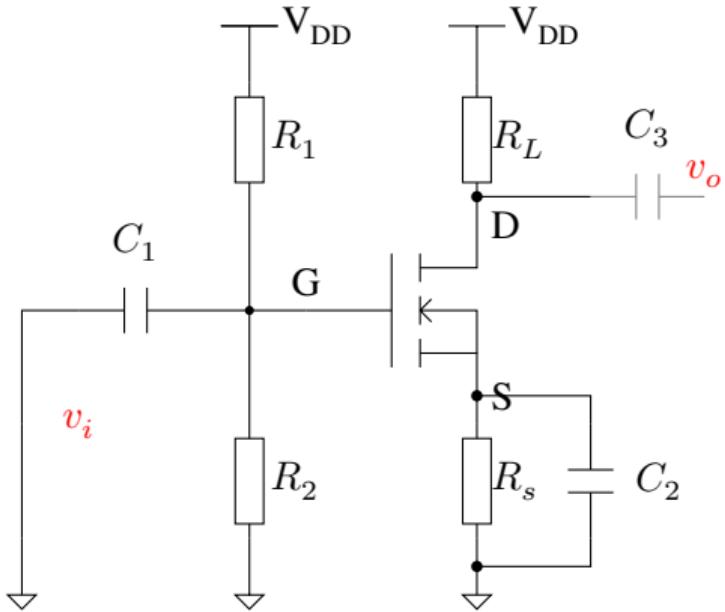

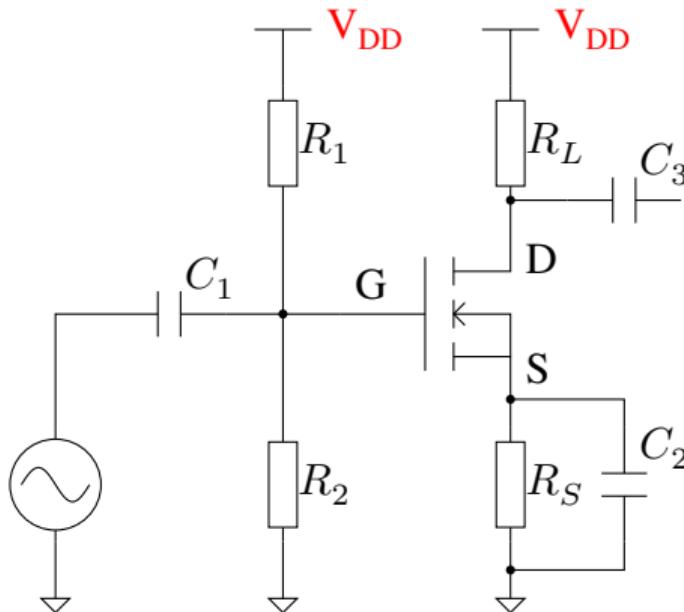

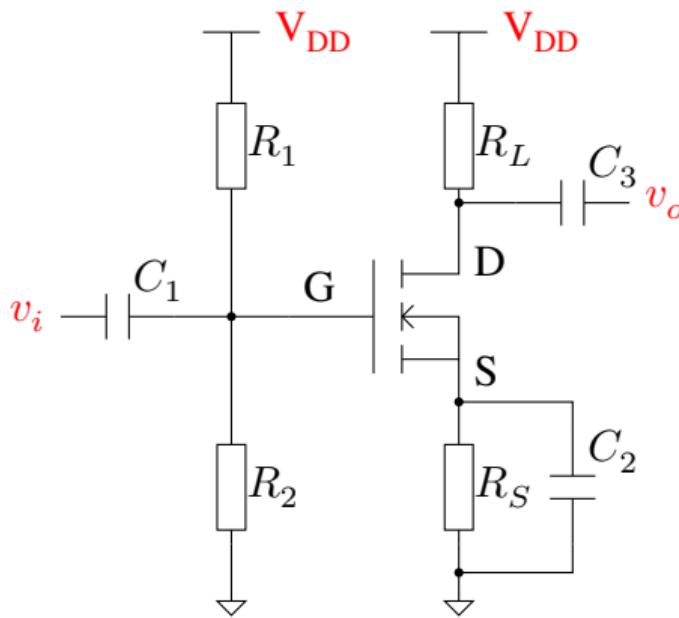

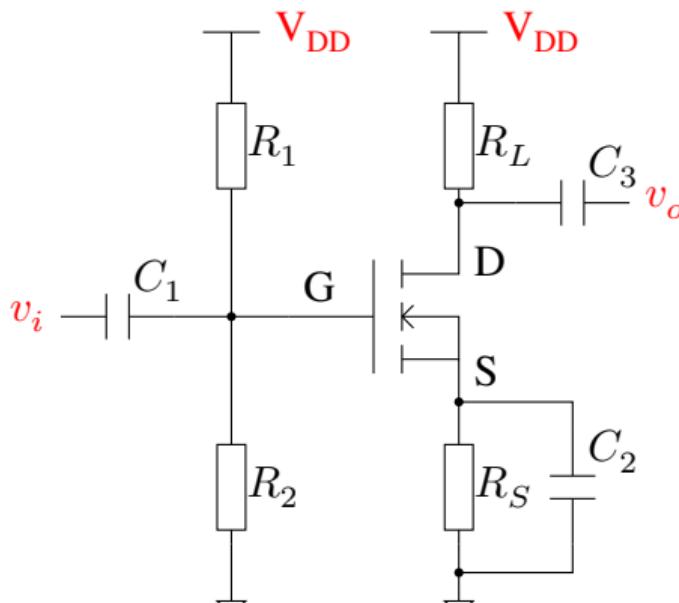

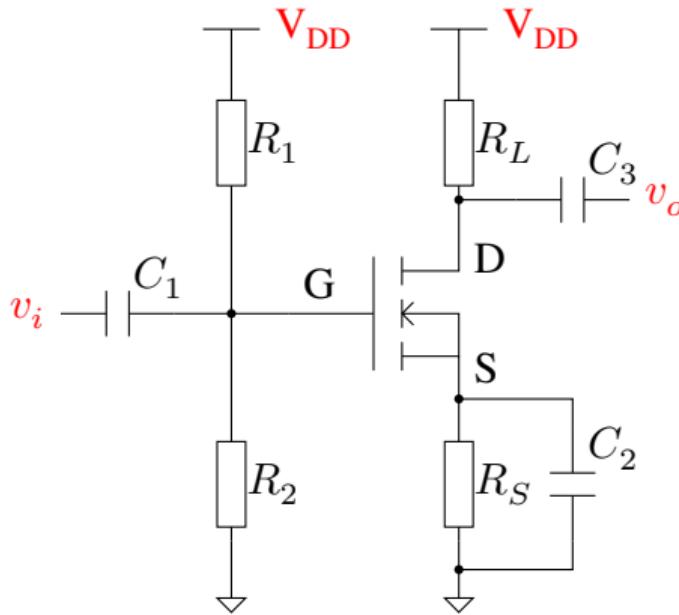

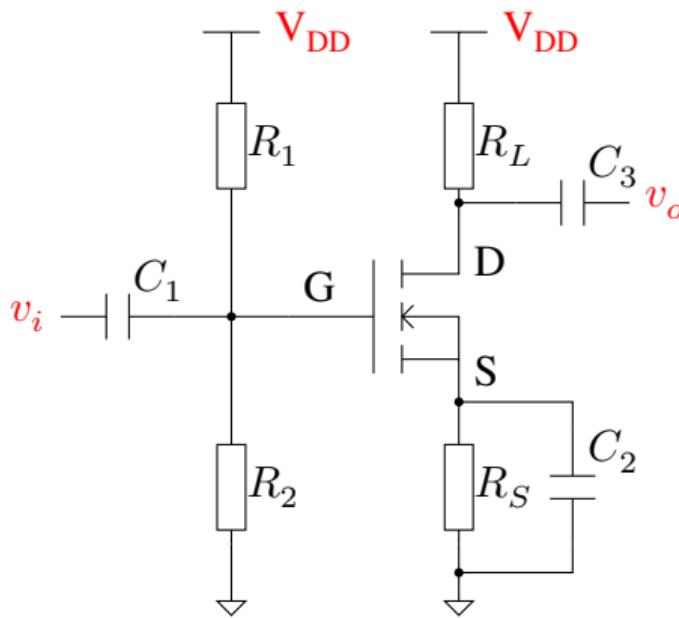

# MOSトランジスタの基本増幅回路

## ソース接地回路の設計

### 設計手順の例 (絶対こうしろという意味ではないです。)

#### ① AC 設計

小信号部分をナレータ・ノレータ

モデル(等)で解析し、

を決める。

#### ② DC 設計

MOSFET が

れるように

にバイアスさ

を設定す

る。(計算は面倒)

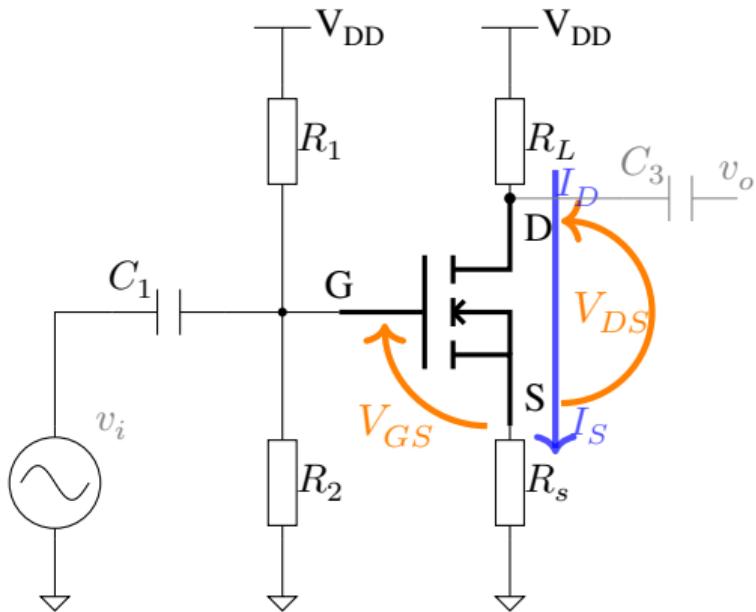

# MOSトランジスタの基本増幅回路

## ソース接地回路の設計

### 設計手順の例 (絶対こうしろという意味ではないです。)

#### ① AC 設計

小信号部分をナレータ・ノレータ

モデル(等)で解析し、

を決める。

#### ② DC 設計

MOSFET が

れるように

にバイアスさ

を設定す

る。(計算は面倒)

# MOSトランジスタの基本増幅回路

## ソース接地回路の設計

### 設計手順の例 (絶対こうしろという意味ではないです。)

#### ① AC 設計

小信号部分をナレータ・ノレータモデル(等)で解析し、 $R_L$ を決める。

#### ② DC 設計

MOSFET が

れるように

る。(計算は面倒)

にバイアスさ

を設定す

# MOSトランジスタの基本増幅回路

## ソース接地回路の設計

### 設計手順の例 (絶対こうしろという意味ではないです。)

#### ① AC 設計

小信号部分をナレータ・ノレータモデル(等)で解析し、 $R_L$ を決める。

#### ② DC 設計

MOSFET が

れるように

る。(計算は面倒)

にバイアスさ

を設定す

# MOSトランジスタの基本増幅回路

## ソース接地回路の設計

### 設計手順の例 (絶対こうしろという意味ではないです。)

#### ① AC 設計

小信号部分をナレータ・ノレータモデル(等)で解析し、 $R_L$ を決める。

#### ② DC 設計

MOSFET が**飽和領域**にバイアスされるように**電流**を設定する。(計算は面倒)

# MOSトランジスタの基本増幅回路

## ソース接地回路の設計

### 設計手順の例 (絶対こうしろという意味ではないです。)

#### ① AC 設計

小信号部分をナレータ・ノレータモデル(等)で解析し、 $R_L$ を決める。

#### ② DC 設計

MOSFET が**飽和領域**にバイアスされるように  $R_1$ ,  $R_2$ ,  $R_s$  を設定する。(計算は面倒)

# MOSトランジスタの基本増幅回路

## ソース接地回路の設計

### 設計手順の例 (絶対こうしろという意味ではないです。)

#### ① AC 設計

小信号部分をナレータ・ノレータモデル(等)で解析し、 $R_L$ を決める。

#### ② DC 設計

MOSFET が**飽和領域**にバイアスされるように  $R_1$ ,  $R_2$ ,  $R_s$  を設定する。(計算は面倒)

とりあえず設計は置いておいて、与えられた回路を読める（解析できる）ようになろう。

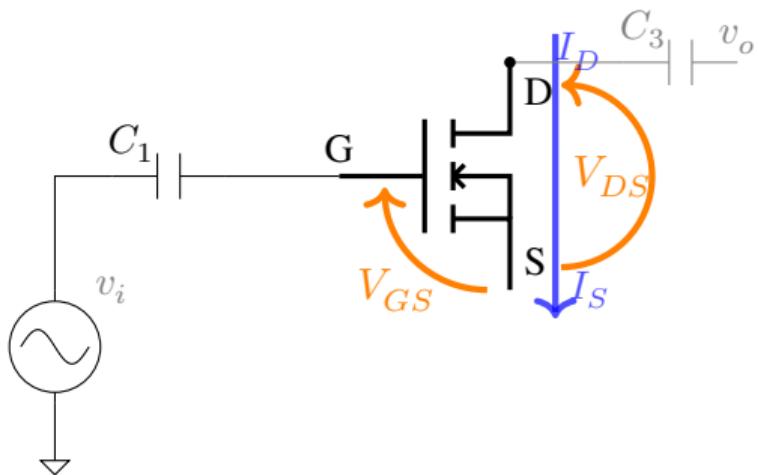

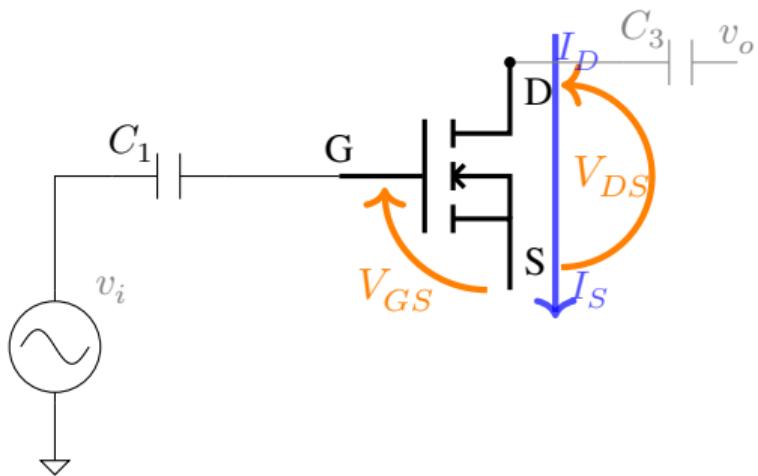

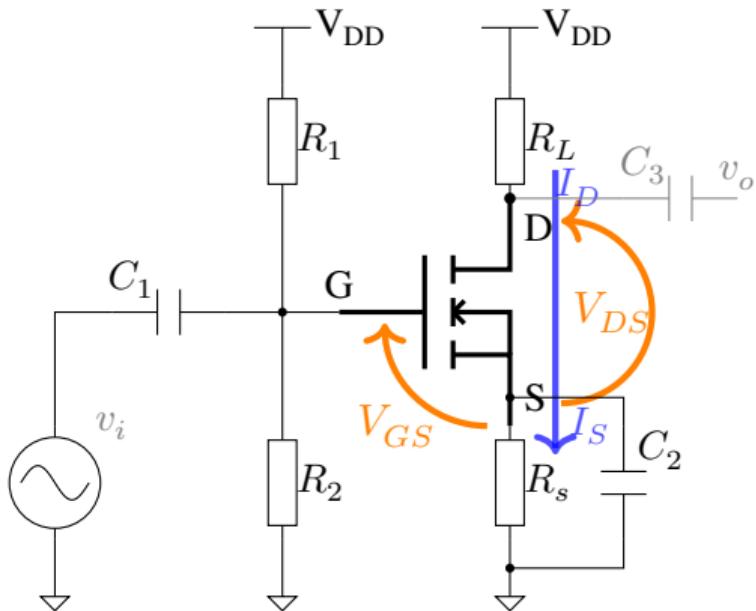

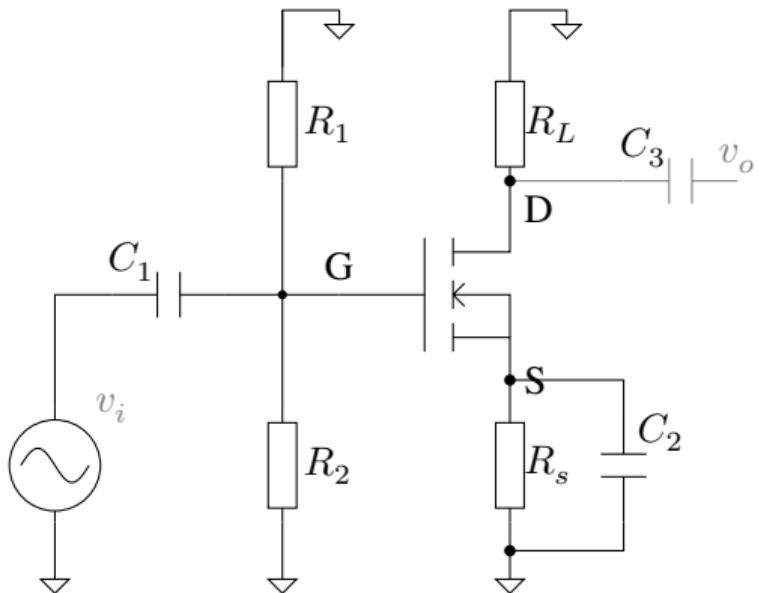

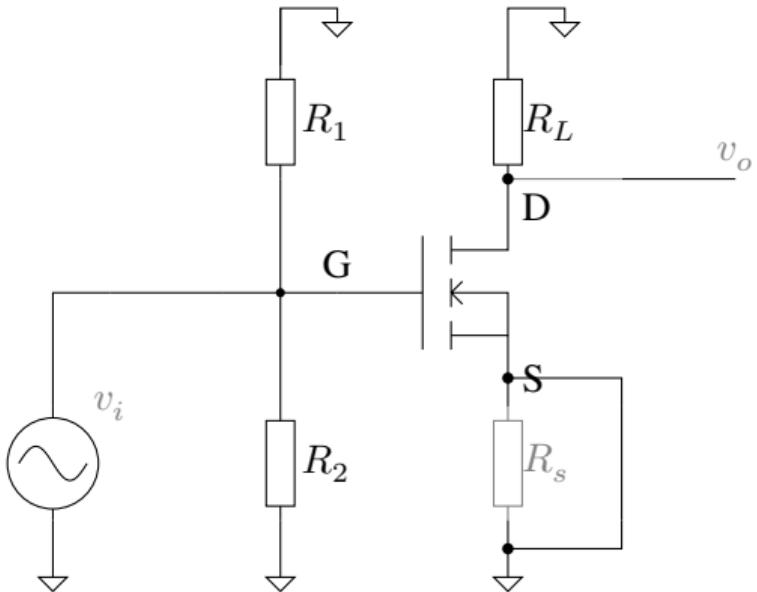

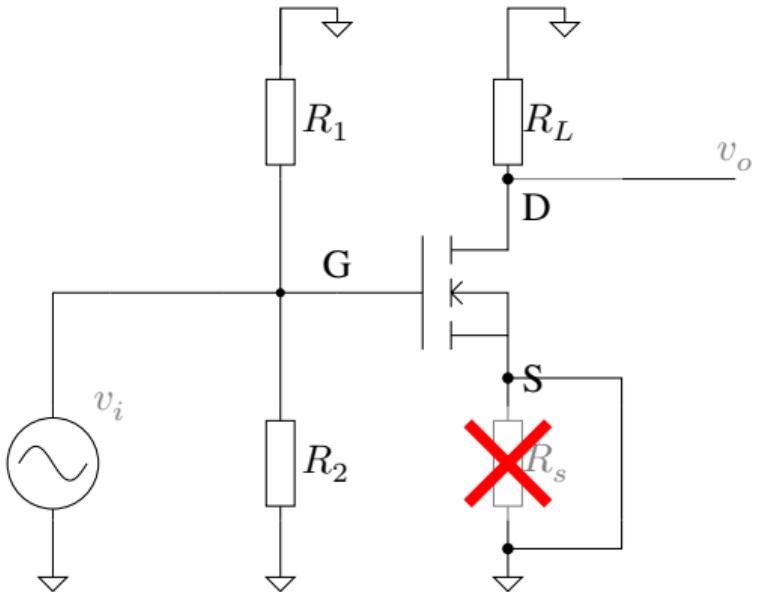

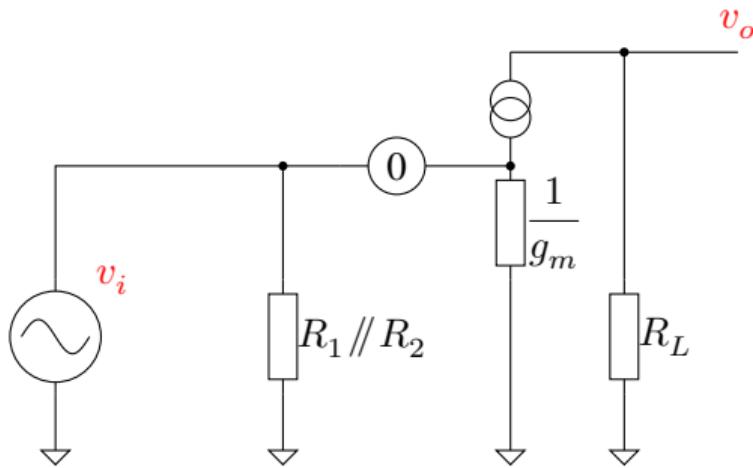

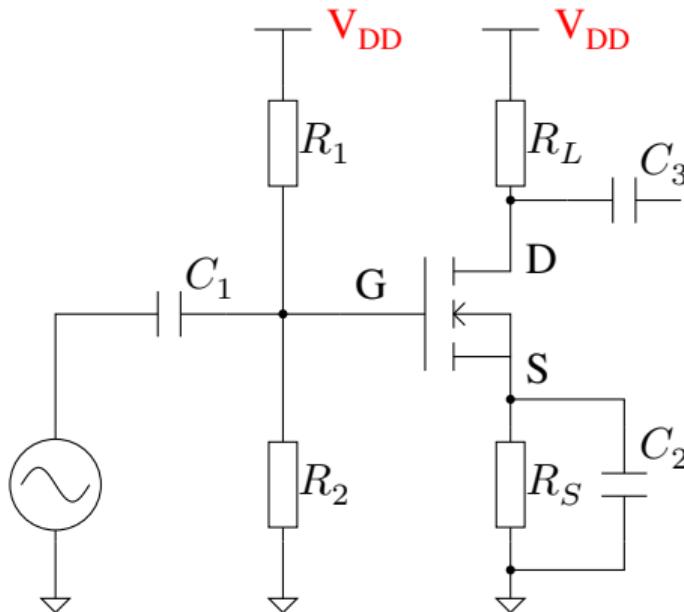

# ソース接地回路の AC 解析の考え方

## AC 解析の準備

- ① 重ねの理の考え方により、 $v_i$  はそのまま、とする。

( $\rightarrow R_1, R_2$  が並列つなぎに見えるようになる。)

- ②  $\omega$  に対して  $C_1, C_2, C_3$  が十分大きい( )とする。

( $\rightarrow R_S$  の意味がなくなる。)

- ③ ゆえに AC については次ページの回路とみなせる。

# ソース接地回路の AC 解析の考え方

## AC 解析の準備

- ① 重ねの理の考え方により、 $v_i$  **はそのまま**、 $V_{DD} = 0$ とする。

( $\rightarrow R_1, R_2$  が並列つなぎに見えるようになる。)

- ②  $\omega$  に対して  $C_1, C_2, C_3$  が十分大きい( )とする。

( $\rightarrow R_S$  の意味がなくなる。)

- ③ ゆえに AC については次ページの回路とみなせる。

## AC 解析の準備

- ① 重ねの理の考え方により、 $v_i$  **はそのまま、 $V_{DD} = 0$** とする。

( $\rightarrow R_1, R_2$  が並列つなぎに見えるようになる。)

- ②  $\omega$  に対して  $C_1, C_2, C_3$  が十分大きい ( $1/j\omega C_i \simeq 0$ ) とする。

( $\rightarrow R_S$  の意味がなくなる。)

- ③ ゆえに AC については次ページの回路とみなせる。

# ソース接地回路の AC 解析の考え方

## AC 解析の準備

- ① 重ねの理の考え方により、 $v_i$  **はそのまま**、 $V_{DD} = 0$ とする。

( $\rightarrow R_1, R_2$  が並列つなぎに見えるようになる。)

- ②  $\omega$  に対して  $C_1, C_2, C_3$  が十分大きい ( $1/j\omega C_i \simeq 0$ ) とする。

( $\rightarrow R_S$  の意味がなくなる。)

- ③ ゆえに AC については次ページの回路とみなせる。

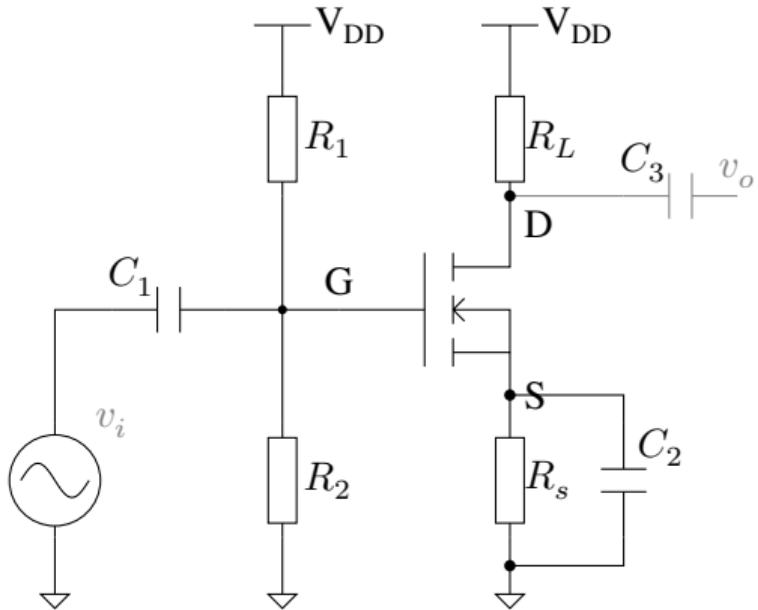

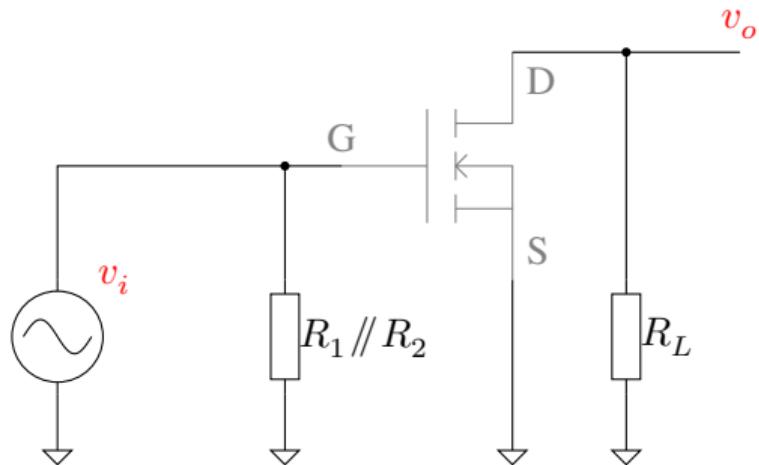

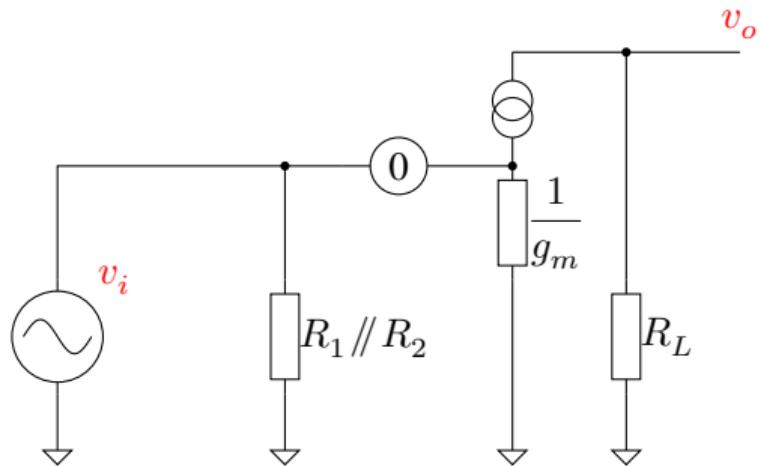

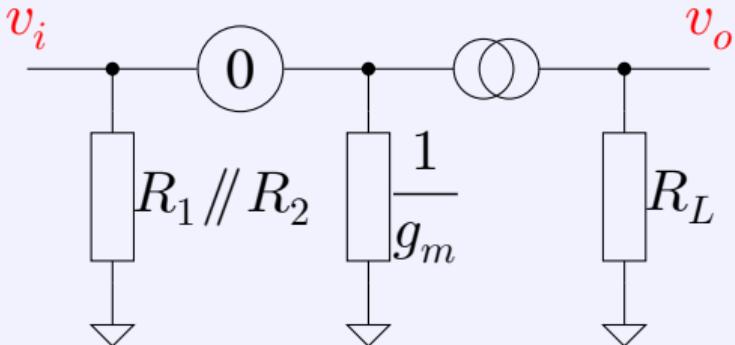

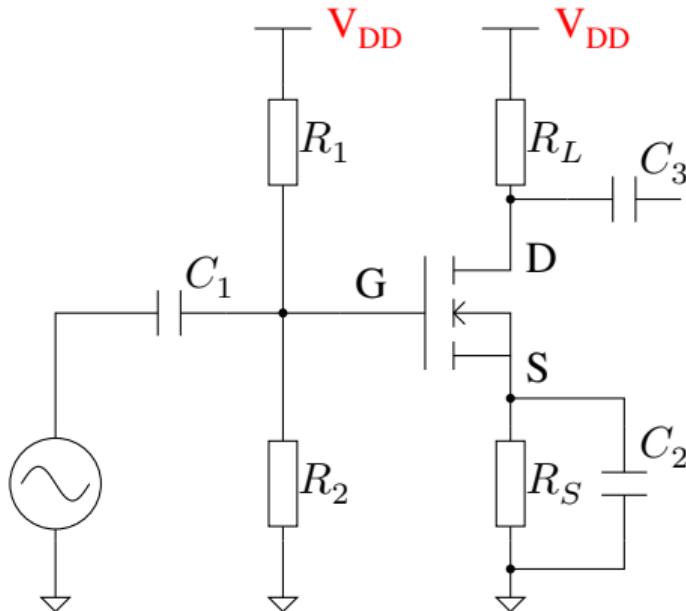

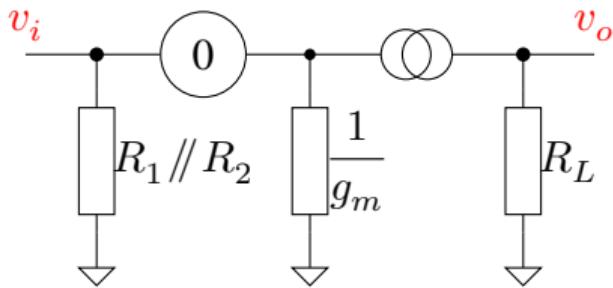

# ソース接地回路の AC 解析 (déjà vu?)

## さらに図を整理

問:  $v_o$  と  $v_i$  の比、**電圧利得**

$A_v \triangleq v_o/v_i$  を求めよ。

# ソース接地回路の AC 解析 (déjà vu?)

さらに図を整理

問:  $v_o$  と  $v_i$  の比、**電圧利得**

$A_v \triangleq v_o/v_i$  を求めよ。

# ソース接地回路の AC 解析 (déjà vu?)

さらに図を整理

問:  $v_o$  と  $v_i$  の比、**電圧利得**

$A_v \triangleq v_o/v_i$  を求めよ。

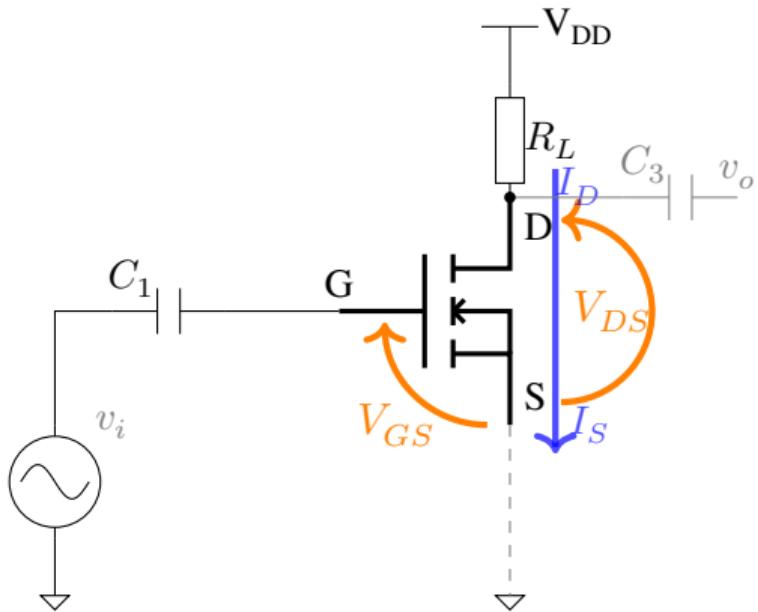

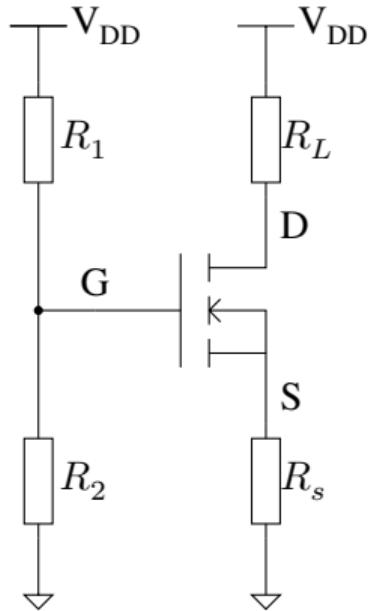

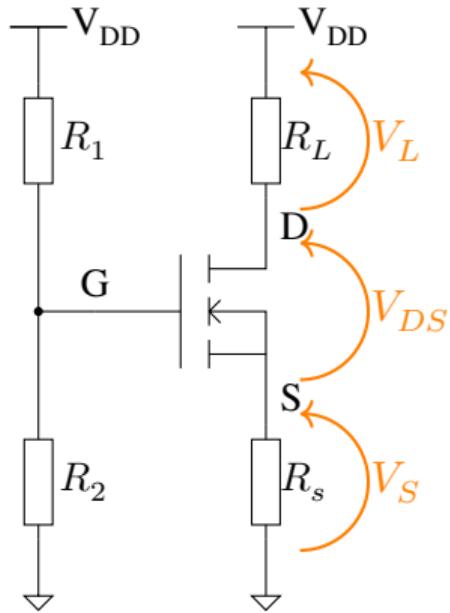

# ソース接地回路の DC 解析の考え方

## DC 解析の準備

- ① 重ねの理の考え方により、 $V_{DD}$  はそのまま、とする。

- ②  $C_1, C_2, C_3$  はといっしょ。

- ③ バイアスが飽和領域であれば  $I_D = K(V_{GS} - V_T)^2$  をトランジスタのモデルとし、方程式を立てて解く。

- ④ バイアス設計の目安として  $V_L$  :  $V_{DS} : V_S = 1 : 1 : 0.1 \sim 0.5$  程度が良いとされている。

## DC 解析の準備

- ① 重ねの理の考え方により、 $V_{DD}$  はそのまま、 $v_i = 0$  とする。

- ②  $C_1, C_2, C_3$  は といっしょ。

- ③ バイアスが飽和領域であれば  $I_D = K(V_{GS} - V_T)^2$  をトランジスタのモデルとし、方程式を立てて解く。

- ④ バイアス設計の目安として  $V_L$  :  $V_{DS} : V_S = 1 : 1 : 0.1 \sim 0.5$  程度が良いとされている。

## DC 解析の準備

- ① 重ねの理の考え方により、 $V_{DD}$  はそのまま、 $v_i = 0$  とする。

- ②  $C_1, C_2, C_3$  は開放といっしょ。

- ③ バイアスが飽和領域であれば  $I_D = K(V_{GS} - V_T)^2$  をトランジスタのモデルとし、方程式を立てて解く。

- ④ バイアス設計の目安として  $V_L$  :  $V_{DS} : V_S = 1 : 1 : 0.1 \sim 0.5$  程度が良いとされている。

# ソース接地回路の DC 解析の考え方

## DC 解析の準備

- ① 重ねの理の考え方により、 $V_{DD}$  はそのまま、 $v_i = 0$  とする。

- ②  $C_1, C_2, C_3$  は開放といっしょ。

- ③ バイアスが飽和領域であれば  $I_D = K(V_{GS} - V_T)^2$  をトランジスタのモデルとし、方程式を立てて解く。

- ④ バイアス設計の目安として  $V_L$  :  $V_{DS} : V_S = 1 : 1 : 0.1 \sim 0.5$  程度が良いとされている。

# 大変めんどくさい練習問題

これまでの総復習といったところ

問:  $V_{DD} = 5 \text{ V}$ ,  $R_1 = 22 \text{ k}\Omega$ ,  $R_2 = 33 \text{ k}\Omega$ ,  $R_L = 22 \text{ k}\Omega$ ,  $R_S = 4.8 \text{ k}\Omega$  で

トランジスタのしきい電圧を  $V_T = 0.52 \text{ V}$ 、トランスコンダクタンス係数を  $K = 25 \mu\text{S/V}$  とする。

- 飽和領域にバイアスされていることを確認せよ。

- トランスコンダクタンス  $g_m$  を求めよ。

# 大変めんどくさい練習問題

これまでの総復習といったところ

問:  $V_{DD} = 5 \text{ V}$ ,  $R_1 = 22 \text{ k}\Omega$ ,  $R_2 = 33 \text{ k}\Omega$ ,  $R_L = 22 \text{ k}\Omega$ ,  $R_S = 4.8 \text{ k}\Omega$  で

トランジスタのしきい電圧を  $V_T = 0.52 \text{ V}$ 、トランスコンダクタンス係数を  $K = 25 \mu\text{S/V}$  とする。

- 飽和領域にバイアスされていることを確認せよ。

- トランスコンダクタンス  $g_m$  を求めよ。

①  $V_{DS} = 2.32 > V_{GS} - V_T = 2$  より飽和領域である。

# 大変めんどくさい練習問題

これまでの総復習といったところ

問:  $V_{DD} = 5 \text{ V}$ ,  $R_1 = 22 \text{ k}\Omega$ ,  $R_2 = 33 \text{ k}\Omega$ ,  $R_L = 22 \text{ k}\Omega$ ,  $R_S = 4.8 \text{ k}\Omega$  で

トランジスタのしきい電圧を  $V_T = 0.52 \text{ V}$ 、トランスコンダクタンス係数を  $K = 25 \mu\text{S/V}$  とする。

- 飽和領域にバイアスされていることを確認せよ。

- トランスコンダクタンス  $g_m$  を求めよ。

①  $V_{DS} = 2.32 > V_{GS} - V_T = 2$  より飽和領域である。

②  $g_m = 2K(V_{GS} - V_T) = 10^{-4} \text{ S}$

# 前ページの問題の文字だけの解説

$V_G = V_{DD}R_2/(R_1 + R_2) = 3$ 。ソース電位を  $V_S$  とすると、飽和領域の特性式より  $I_D = K(V_{GS} - V_T)^2 = 25 \times 10^{-6} \times (3 - V_S - 0.52)^2$ 。一方、 $V_S$  は  $I_D$  を使って  $V_S = R_S I_D = 4800 I_D$  とも表せるのでこれを代入して次の方程式を得る。

$$I_D = 25 \times 10^{-6} \times (3 - 4800 I_D - 0.52)^2 = 25 \times 10^{-6} \times (2.48 - 4800 I_D)^2$$

これを解くと  $I_D = 0.0001$  もしくは  $I_D \approx 0.00267$  であるが、後者だとすると  $R_L$  での電圧降下が  $22000 \times 0.00267 = 58.74$  V になってしまい明らかにおかしい。したがって  $I_D = 0.0001$  となる。以上より  $V_S = 4800 I_D = 0.48$ ,  $V_D = 5 - 22000 I_D = 2.8$  となる。すると  $V_{GS} = V_G - V_S = 3 - 0.48 = 2.52$ ,  $V_{DS} = V_D - V_S = 2.8 - 0.48 = 2.32$  なので飽和領域の条件を満たすことが確認できる。一方バイアス状態が決まれば伝達コンダクタンスは  $\frac{dI_D}{dV_{GS}} = 2K(V_{GS} - V_T) = 0.0001$  と計算できる。

# 入力インピーダンスと出力インピーダンス

一般的には入力インピーダンスは大きい方が、出力インピーダンスは小さい方がよろしいとされています。

**小信号**モデルにおいて、

- 入力側から見たインピーダンスを**入力インピーダンス**といい、

- 出力側から見たインピーダンスを**出力インピーダンス**という。

ただし、 $v_i = 0$ と考える。

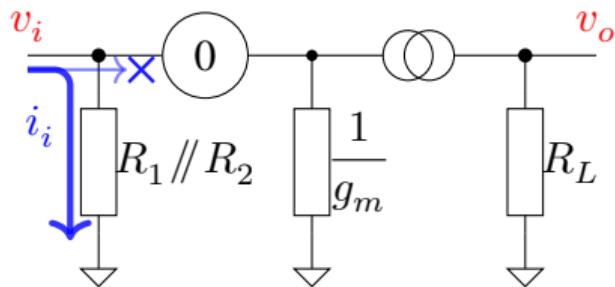

# ソース接地回路の入力インピーダンス

入力側の小信号の電圧と電流の比を計算するだけ。

- 入力側に電圧  $v_i$  を加えると、電流  $i_i$  はすべて  $R_1 \parallel R_2$  に流れる。

- つまり入力インピーダンス  $Z_i = v_i/i_i$  は単純に、

# ソース接地回路の入力インピーダンス

入力側の小信号の電圧と電流の比を計算するだけ。

- 入力側に電圧  $v_i$  を加えると、電流  $i_i$  はすべて  $R_1 \parallel R_2$  に流れる。

- つまり入力インピーダンス  $Z_i = v_i/i_i$  は単純に、 $R_1 \parallel R_2$ 。

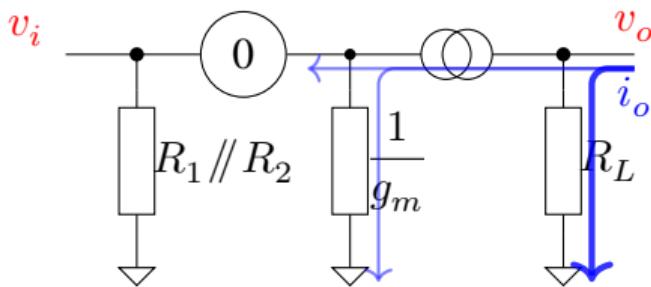

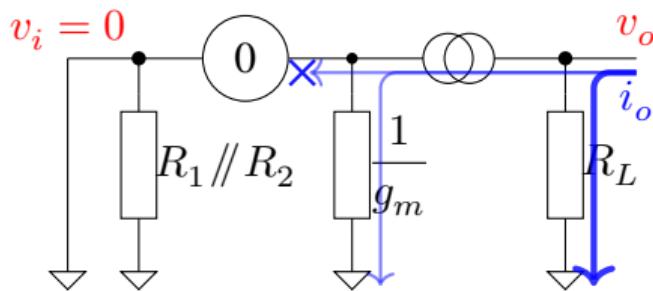

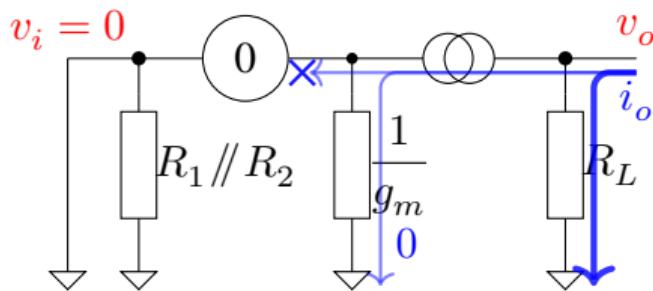

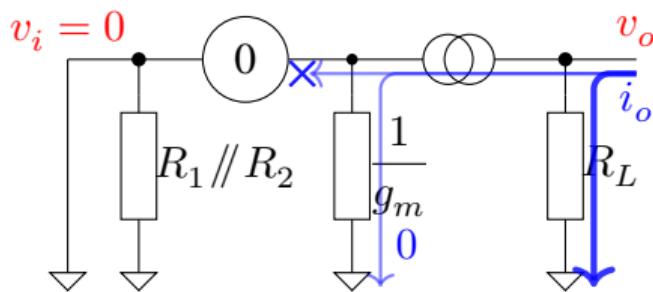

# ソース接地回路の出力インピーダンス

入力を 0 と仮定して考える。

- $v_i$  は小信号、つまり「変化分」なので開放はあり得ない。出力インピーダンスを考えるときは  $v_i = 0$  を仮定する。

- そして、出力に  $v_o$  を印加したと仮定して、 $i_o$  を計算し、出力インピーダンス  $Z_o = v_o/i_o$  を求める。

- この場合ナレータに電流は流れず、 $1/g_m$  の抵抗の電圧が 0 なのでそこにも電流が流れない。結局  $i_o$  はすべて  $R_L$  を流れるので  $Z_o = R_L$  。

# ソース接地回路の出力インピーダンス

入力を 0 と仮定して考える。

- $v_i$  は小信号、つまり「変化分」なので開放はあり得ない。出力インピーダンスを考えるときは  $v_i = 0$  を仮定する。

- そして、出力に  $v_o$  を印加したと仮定して、 $i_o$  を計算し、出力インピーダンス  $Z_o = v_o/i_o$  を求める。

- この場合ナレータに電流は流れず、 $1/g_m$  の抵抗の電圧が 0 なのでそこにも電流が流れない。結局  $i_o$  はすべて  $R_L$  を流れるので  $Z_o = \dots$ 。

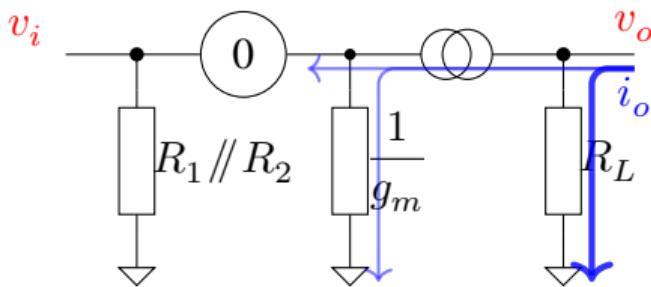

# ソース接地回路の出力インピーダンス

入力を 0 と仮定して考える。

- $v_i$  は小信号、つまり「変化分」なので開放はあり得ない。出力インピーダンスを考えるときは  $v_i = 0$  を仮定する。

- そして、出力に  $v_o$  を印加したと仮定して、 $i_o$  を計算し、出力インピーダンス  $Z_o = v_o/i_o$  を求める。

- この場合ナレータに電流は流れず、 $1/g_m$  の抵抗の電圧が 0 なのでそこにも電流が流れない。結局  $i_o$  はすべて  $R_L$  を流れるので  $Z_o = \dots$ 。

# ソース接地回路の出力インピーダンス

入力を 0 と仮定して考える。

- $v_i$  は小信号、つまり「変化分」なので開放はあり得ない。出力インピーダンスを考えるときは  $v_i = 0$  を仮定する。

- そして、出力に  $v_o$  を印加したと仮定して、 $i_o$  を計算し、出力インピーダンス  $Z_o = v_o/i_o$  を求める。

- この場合ナレータに電流は流れず、 $1/g_m$  の抵抗の電圧が 0 なのでそこにも電流が流れない。結局  $i_o$  はすべて  $R_L$  を流れるので  $Z_o = \dots$ 。

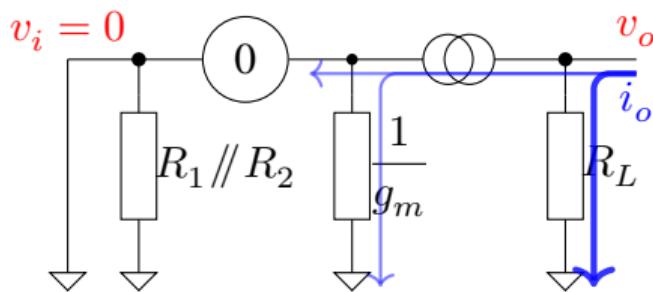

# ソース接地回路の出力インピーダンス

入力を 0 と仮定して考える。

- $v_i$  は小信号、つまり「変化分」なので開放はあり得ない。出力インピーダンスを考えるときは  $v_i = 0$  を仮定する。

- そして、出力に  $v_o$  を印加したと仮定して、 $i_o$  を計算し、出力インピーダンス  $Z_o = v_o/i_o$  を求める。

- この場合ナレータに電流は流れず、 $1/g_m$  の抵抗の電圧が 0 なのでそこにも電流が流れない。結局  $i_o$  はすべて  $R_L$  を流れるので  $Z_o = \dots$ 。

# ソース接地回路の出力インピーダンス

入力を 0 と仮定して考える。

- $v_i$  は小信号、つまり「変化分」なので開放はあり得ない。出力インピーダンスを考えるときは  $v_i = 0$  を仮定する。

- そして、出力に  $v_o$  を印加したと仮定して、 $i_o$  を計算し、出力インピーダンス  $Z_o = v_o/i_o$  を求める。

- この場合ナレータに電流は流れず、 $1/g_m$  の抵抗の電圧が 0 なのでそこにも電流が流れない。結局  $i_o$  はすべて  $R_L$  を流れるので  $Z_o = R_L$ 。

# 絶対解けないとまずい練習問題

ストーリィ的には数ページ前のめんどくさい練習問題の続き

問:  $V_{DD} = 5 \text{ V}$ ,  $R_1 = 22 \text{ k}\Omega$ ,  $R_2 = 33 \text{ k}\Omega$ ,  $R_L = 22 \text{ k}\Omega$ ,  $R_S = 4.8 \text{ k}\Omega$  で

トランジスタのトランスコンダクタンスが  $g_m = 10^{-4} \text{ S}$  のとき、

- 電圧利得  $A_v = v_o/v_i$

- 入力インピーダンス  $Z_i$

- 出力インピーダンス  $Z_o$

を求めよ。

# 絶対解けないとまずい練習問題

ストーリィ的には数ページ前のめんどくさい練習問題の続き

- $A_v = -g_m R_L = -2.2$

問:  $V_{DD} = 5 \text{ V}$ ,  $R_1 = 22 \text{ k}\Omega$ ,  $R_2 = 33 \text{ k}\Omega$ ,  $R_L = 22 \text{ k}\Omega$ ,  $R_S = 4.8 \text{ k}\Omega$  でトランジスタのトランスコンダクタンスが  $g_m = 10^{-4} \text{ S}$  のとき、

- 電圧利得  $A_v = v_o/v_i$

- 入力インピーダンス  $Z_i$

- 出力インピーダンス  $Z_o$

を求めよ。

# 絶対解けないとまずい練習問題

ストーリィ的には数ページ前のめんどくさい練習問題の続き

- $A_v = -g_m R_L = -2.2$

- $Z_i = R_1 // R_2 = 13.2 \times 10^3 \Omega$

問:  $V_{DD} = 5 \text{ V}$ ,  $R_1 = 22 \text{ k}\Omega$ ,  $R_2 = 33 \text{ k}\Omega$ ,  $R_L = 22 \text{ k}\Omega$ ,  $R_S = 4.8 \text{ k}\Omega$  でトランジスタのトランスコンダクタンスが  $g_m = 10^{-4} \text{ S}$  のとき、

- 電圧利得  $A_v = v_o/v_i$

- 入力インピーダンス  $Z_i$

- 出力インピーダンス  $Z_o$

を求めよ。

# 絶対解けないとまずい練習問題

ストーリィ的には数ページ前のめんどくさい練習問題の続き

- $A_v = -g_m R_L = -2.2$

- $Z_i = R_1 // R_2 = 13.2 \times 10^3 \Omega$

- $Z_o = R_L = 22 \times 10^3 \Omega$

問:  $V_{DD} = 5 \text{ V}$ ,  $R_1 = 22 \text{ k}\Omega$ ,  $R_2 = 33 \text{ k}\Omega$ ,  $R_L = 22 \text{ k}\Omega$ ,  $R_S = 4.8 \text{ k}\Omega$  でトランジスタのトランスコンダクタンスが  $g_m = 10^{-4} \text{ S}$  のとき、

- 電圧利得  $A_v = v_o/v_i$

- 入力インピーダンス  $Z_i$

- 出力インピーダンス  $Z_o$

を求めよ。

# ミニレポート課題 (受付期間: 授業当日～次回授業の前日)

受付期間外には提出しないこと。(自動処理しています。)

p. 19 の問題を解け。答えのみではなく、**きちんとした説明をつけること**。以下の語をそれぞれ一度以上使うこと。

ゲート, ソース, ドレイン, ナレータ, ノレータ, 重ねの理 (重ね合わせの理), キャパシタ

提出は下記 URL の Google Forms。歪んでいない、開いた時に横倒しになっていない、コントラストが読むに耐えうる PDF で提出すること。**手書きを写真撮影する場合はスキャナもしくはスキャナアプリの使用を必須とする。**

<https://forms.gle/MpUmErDi6qk8GSUC6>