# アナログ電子回路

授業開始までしばらくお待ちください。

- 講義資料（スライド等）は Google drive に置く。授業前には虫喰い状態のスライドのみを提供するが、授業後に穴埋め版を uncovered フォルダに置くので復習に活用されたい。

<https://drive.google.com/drive/folders/1yzIsRZsVGFErhnfzn8Hycsn6nRPNCczn>

- 授業の録画も同じところに置く。

- ミニレポートは **Google Forms**

(<https://forms.gle/MpUmErDi6qk8GSUC6>) に提出。

- 出席は UNIPA で取るが、出席そのものは評価せず。極論するとテストのみ出席で他は全欠席でも A 評価はあり得る。なお、**不正出席をした場合は 21 点の減点**とする。

- 基本的には**中間演習**と**期末試験**で評価。

- 毎回ミニレポートを課す。出す者は提出期間を厳守すること。

- 試験の不合格者は**毎回のミニレポートと出席**で少し救済する。

(しっかりした内容のミニレポートを概ね 9 割以上提出し、かつ UNIPA で 8 割以上遅刻せず出席していた場合最大 10 点程度の救済。提出数や出席数が少ない場合は救済幅が縮小する。いずれかが 7 割を下回ったら一切救済しない。締め切り後の提出は認めない。)

- スライド穴埋め版はその回の授業終了後に公開。

- 授業中に**スライドの誤りを見つけて指摘してくれた者には、誤り一箇所につき先着一名様限り 100 点満点 1 点相当の加点を行う。(ただしごく軽微なものなど、内容によっては加点しない場合もあり。)

2025

# S科アナログ電子回路

Analog Electronics

## 『○○接地増幅回路』

小林裕之

大阪工業大学 RD 学部システムデザイン工学科

OSAKA INSTITUTE OF TECHNOLOGY

7 of 14

a L<sup>A</sup>T<sub>E</sub>X + Beamer slideshow

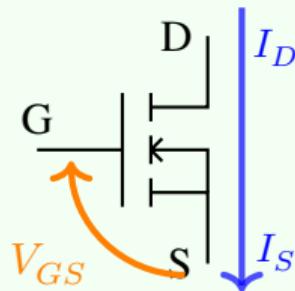

# トランジスタの重要な式の復習 (MOS)

暗記する必要はないけれど考え方を理解しよう。

## MOSFET の特性 (飽和領域)

$$I_D(V_{GS}) = K(V_{GS} - V_T)^2$$

$$g_m = \frac{dI_D}{dV_{GS}}$$

## バイアスの目的・ポイント

- 飽和領域にする。

- $V_{GS}$  を適切な大きさにする。 $(I_D, g_m$  が決まる。)

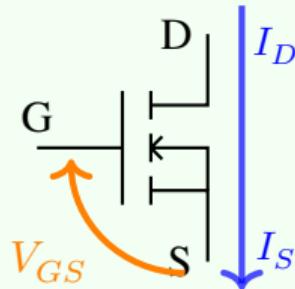

# トランジスタの重要な式の復習 (MOS)

暗記する必要はないけれど考え方を理解しよう。

## MOSFET の特性 (飽和領域)

$$I_D(V_{GS}) = K(V_{GS} - V_T)^2$$

$$g_m = \frac{dI_D}{dV_{GS}} = 2K(V_{GS} - V_T)$$

## バイアスの目的・ポイント

- 飽和領域にする。

- $V_{GS}$  を適切な大きさにする。 $(I_D, g_m$  が決まる。)

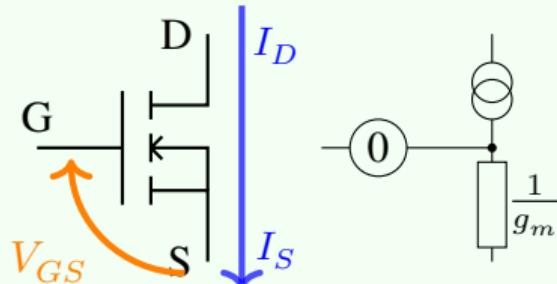

# トランジスタの重要な式の復習 (MOS)

暗記する必要はないけれど考え方を理解しよう。

## MOSFET の特性 (飽和領域)

$$I_D(V_{GS}) = K(V_{GS} - V_T)^2$$

$$g_m = \frac{dI_D}{dV_{GS}} = 2K(V_{GS} - V_T)$$

## バイアスの目的・ポイント

- 飽和領域にする。

- $V_{GS}$  を適切な大きさにする。 $(I_D, g_m$  が決まる。)

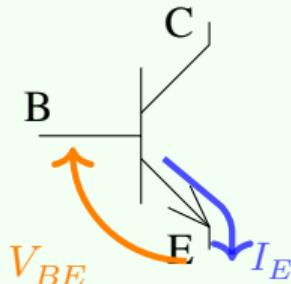

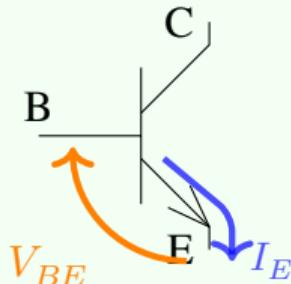

# トランジスタの重要な式の復習 (バイポーラ)

暗記する必要はないけれど考え方を理解しよう。

## bipolar トランジスタの特性

$$I_E = I_{ES} \left\{ \exp \left( \frac{qV_{BE}}{kT} - 1 \right) \right\}$$

$$g_m = \frac{dI_E}{dV_{BE}}$$

## バイアスの目的・ポイント

- BE 間を順方向、BC 間を逆方向に電圧をかける。

- $V_{BE}$  を適切な大きさにする。 $(I_E, g_m)$  が決まる。)

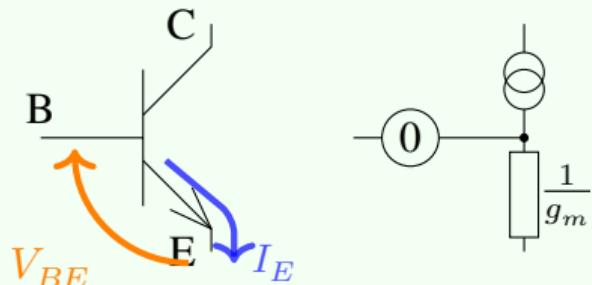

# トランジスタの重要な式の復習 (バイポーラ)

暗記する必要はないけれど考え方を理解しよう。

## bipolar トランジスタの特性

$$I_E = I_{ES} \left\{ \exp \left( \frac{qV_{BE}}{kT} - 1 \right) \right\}$$

$$g_m = \frac{dI_E}{dV_{BE}} = I_{ES} \frac{q}{kT} e^{\frac{qV_{BE}}{kT}} \left( \simeq \frac{qI_E}{kT} \right)$$

## バイアスの目的・ポイント

- BE 間を順方向、BC 間を逆方向に電圧をかける。

- $V_{BE}$  を適切な大きさにする。 $(I_E, g_m)$  が決まる。)

# トランジスタの重要な式の復習 (バイポーラ)

暗記する必要はないけれど考え方を理解しよう。

## bipolar トランジスタの特性

$$I_E = I_{ES} \left\{ \exp \left( \frac{qV_{BE}}{kT} - 1 \right) \right\}$$

$$g_m = \frac{dI_E}{dV_{BE}} = I_{ES} \frac{q}{kT} e^{\frac{qV_{BE}}{kT}} \left( \simeq \frac{qI_E}{kT} \right)$$

## バイアスの目的・ポイント

- BE 間を順方向、BC 間を逆方向に電圧をかける。

- $V_{BE}$  を適切な大きさにする。 $(I_E, g_m)$  が決まる。)

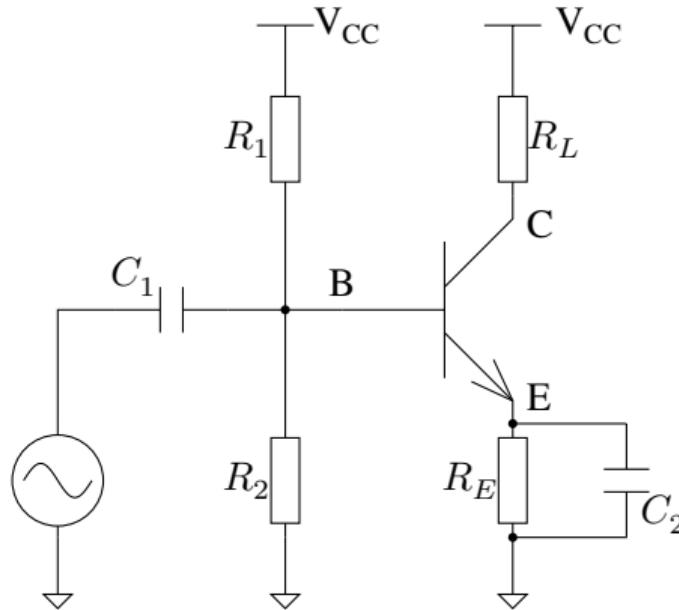

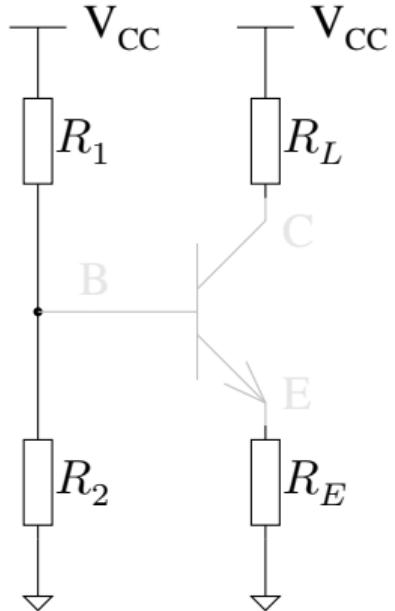

# バイポーラトランジスタの基本増幅回路

## エミッタ接地回路の設計

### 設計手順の例 (絶対こうしろという意味ではないです。)

#### ① AC 設計

小信号部分をナレータ・ノレータモデル(等)で解析し、

を決める。

#### ② DC 設計

適切な

にバイアス抵抗

する。(ナレータ・ノレータモデル

を使ってもいい。)

# バイポーラトランジスタの基本増幅回路

## エミッタ接地回路の設計

### 設計手順の例 (絶対こうしろという意味ではないです。)

#### ① AC 設計

小信号部分をナレータ・ノレータモデル(等)で解析し、 $R_L$ を決める。

#### ② DC 設計

適切な

にバイアス抵抗

する。(ナレータ・ノレータモデル

を使ってもいい。)

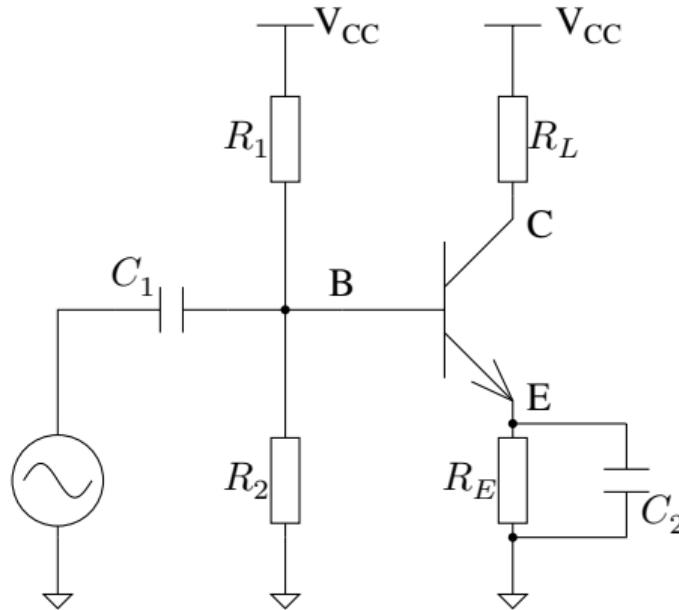

# バイポーラトランジスタの基本増幅回路

## エミッタ接地回路の設計

### 設計手順の例 (絶対こうしろという意味ではないです。)

#### ① AC 設計

小信号部分をナレータ・ノレータモデル(等)で解析し、 $R_L$ を決める。

#### ② DC 設計

適切な**エミッタ電流**が流れるよう

にバイアス抵抗  $R_E$  を設定

する。(ナレータ・ノレータモデル

を使ってもいい。)

# バイポーラトランジスタの基本増幅回路

## エミッタ接地回路の設計

### 設計手順の例 (絶対こうしろという意味ではないです。)

#### ① AC 設計

小信号部分をナレータ・ノレータモデル(等)で解析し、 $R_L$ を決める。

#### ② DC 設計

適切な**エミッタ電流**が流れるよう

にバイアス抵抗 $R_1$ ,  $R_2$ ,  $R_E$ を設定

する。(ナレータ・ノレータモデル

を使ってもいい。)

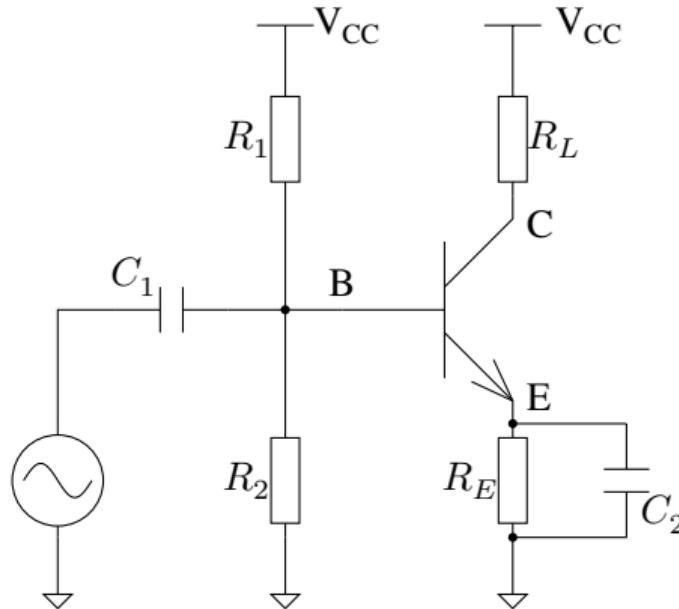

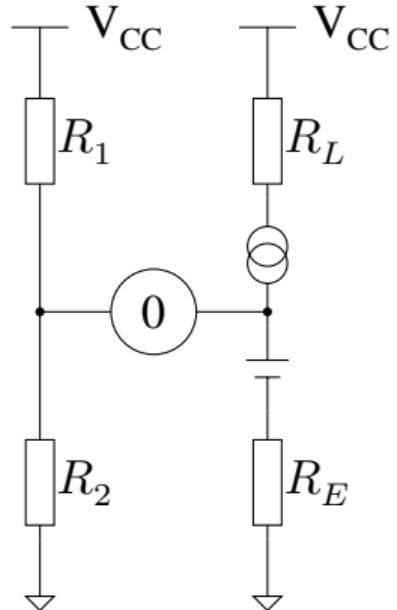

# エミッタ接地回路の AC 解析の考え方

# エミッタ接地回路の AC 解析の考え方

MOS といっしょにつき省略

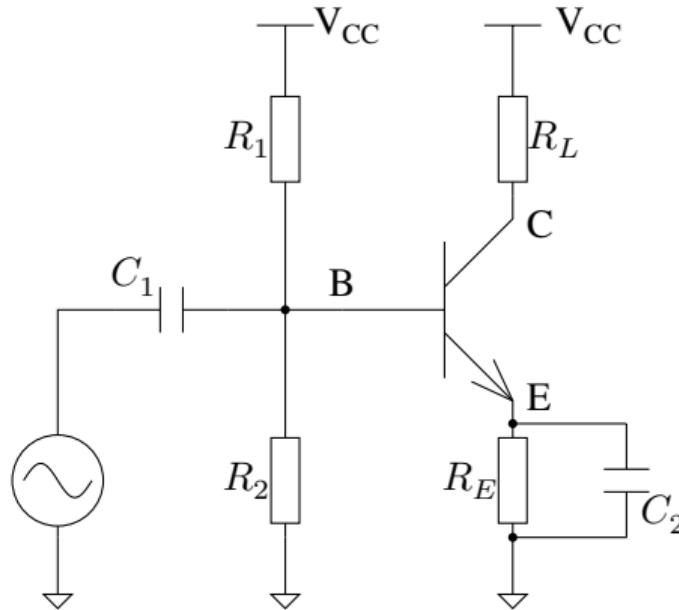

# エミッタ接地回路の DC 解析の考え方兼練習問題

問:  $R_1 = 12 \text{ k}\Omega$ ,  $R_2 = 18 \text{ k}\Omega$ ,  $R_L = 33 \text{ k}\Omega$ ,  $V_{CC} = 3.0 \text{ V}$  であり、大信号モデルにおいて  $V_{BE} = 0.7 \text{ V}$  とする。

- ① DC 解析より  $V_E$  を求めよ。また、コレクタ電位を  $2.25 \text{ V}$  にするための  $R_E$  を求めよ。

- ② 伝達コンダクタンスがエミッタ電流  $I_E$  を使って  $g_m \simeq \frac{qI_E}{kT} \simeq 44I_E$  であるとして  $g_m$  を求めよ。

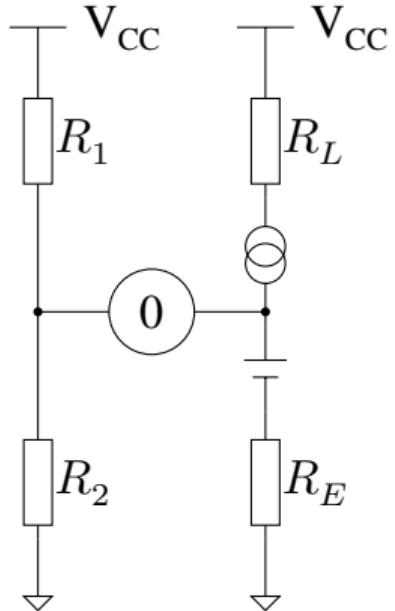

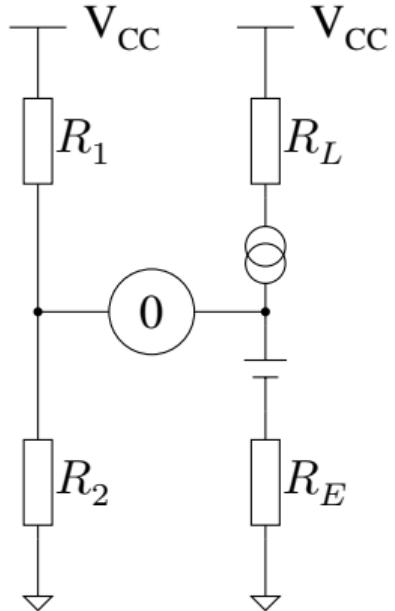

# エミッタ接地回路の DC 解析の考え方兼練習問題

問:  $R_1 = 12 \text{ k}\Omega$ ,  $R_2 = 18 \text{ k}\Omega$ ,  $R_L = 33 \text{ k}\Omega$ ,  $V_{CC} = 3.0 \text{ V}$  であり、大信号モデルにおいて  $V_{BE} = 0.7 \text{ V}$  とする。

- ① DC 解析より  $V_E$  を求めよ。また、コレクタ電位を  $2.25 \text{ V}$  にするための  $R_E$  を求めよ。

- ② 伝達コンダクタンスがエミッタ電流  $I_E$  を使って  $g_m \simeq \frac{qI_E}{kT} \simeq 44I_E$  であるとして  $g_m$  を求めよ。

# エミッタ接地回路の DC 解析の考え方兼練習問題

問:  $R_1 = 12 \text{ k}\Omega$ ,  $R_2 = 18 \text{ k}\Omega$ ,  $R_L = 33 \text{ k}\Omega$ ,  $V_{CC} = 3.0 \text{ V}$  であり、大信号モデルにおいて  $V_{BE} = 0.7 \text{ V}$  とする。

- ① DC 解析より  $V_E$  を求めよ。また、コレクタ電位を  $2.25 \text{ V}$  にするための  $R_E$  を求めよ。

- ② 伝達コンダクタンスがエミッタ電流  $I_E$  を使って  $g_m \simeq \frac{qI_E}{kT} \simeq 44I_E$  であるとして  $g_m$  を求めよ。

$$V_E = 1.1, R_E = 48.4 \times 10^3,$$

# エミッタ接地回路の DC 解析の考え方兼練習問題

問:  $R_1 = 12 \text{ k}\Omega$ ,  $R_2 = 18 \text{ k}\Omega$ ,  $R_L = 33 \text{ k}\Omega$ ,  $V_{CC} = 3.0 \text{ V}$  であり、大信号モデルにおいて  $V_{BE} = 0.7 \text{ V}$  とする。

- ① DC 解析より  $V_E$  を求めよ。また、コレクタ電位を  $2.25 \text{ V}$  にするための  $R_E$  を求めよ。

- ② 伝達コンダクタンスがエミッタ電流  $I_E$  を使って  $g_m \simeq \frac{qI_E}{kT} \simeq 44I_E$  であるとして  $g_m$  を求めよ。

$$V_E = 1.1, R_E = 48.4 \times 10^3, g_m = 0.001$$

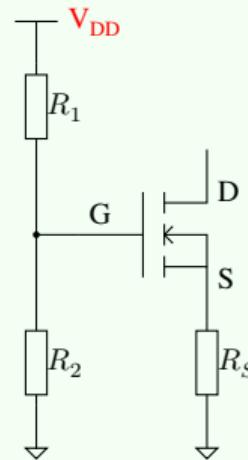

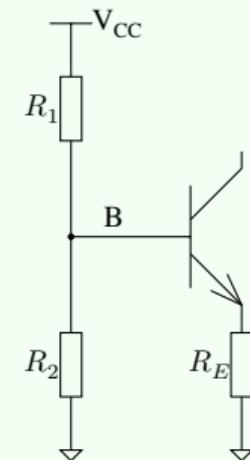

# 基本増幅回路の考え方 (?)

覚えるのは大変。だけどこうすれば自然とわかる!?

必要最小限のバイアスをかける回路がある。譲れない部分なのでこ

こだけは共通としよう。 $(R_S, R_E$  はなくてもいいと言えばいいのですが、入れておくとちょ

っとしたご利益があるので入れておきます。詳細はこの授業の最後の方で……。)

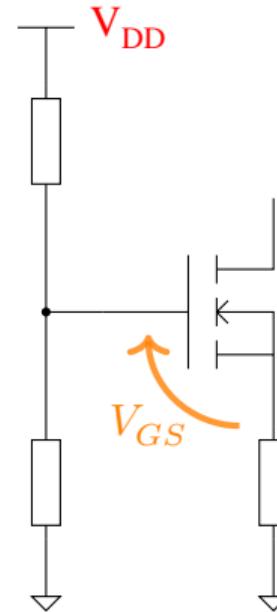

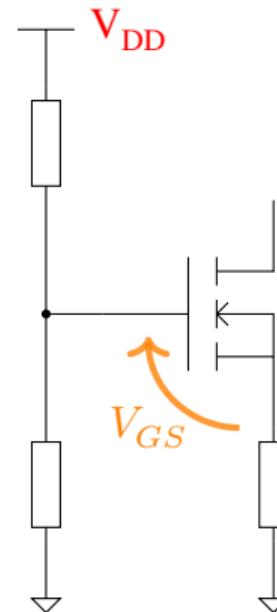

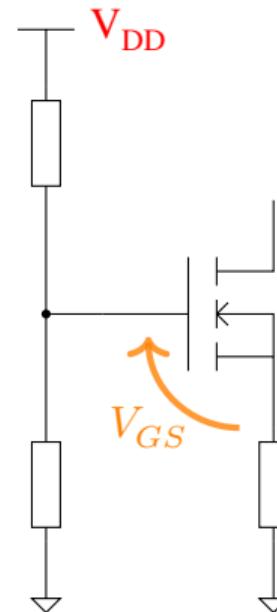

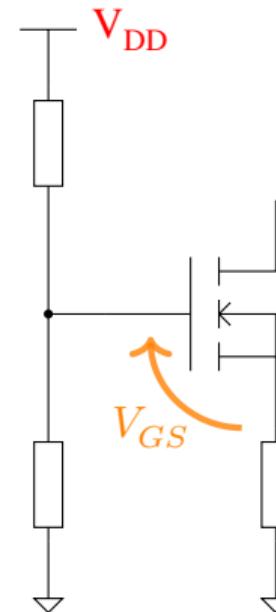

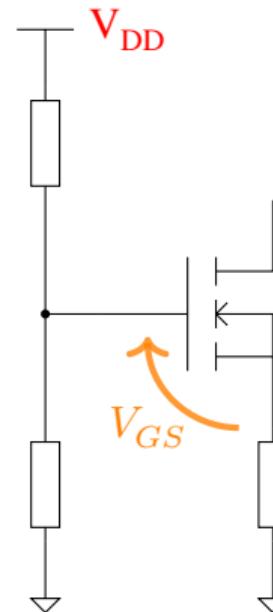

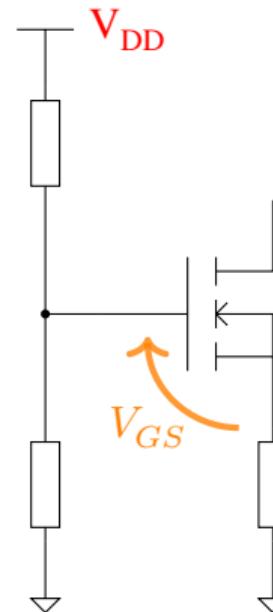

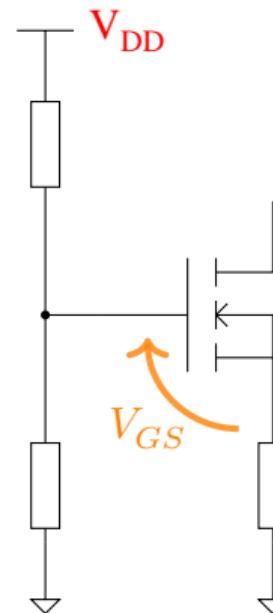

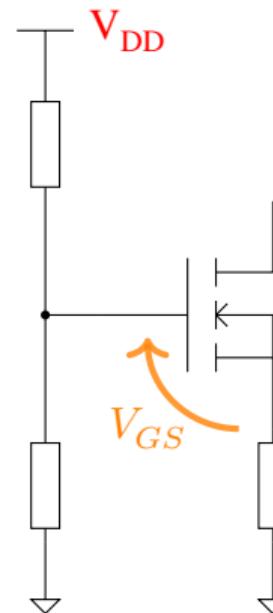

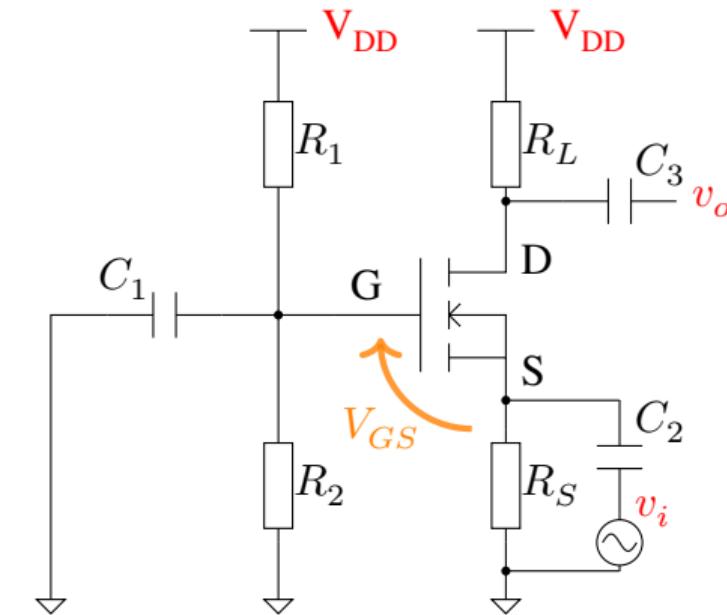

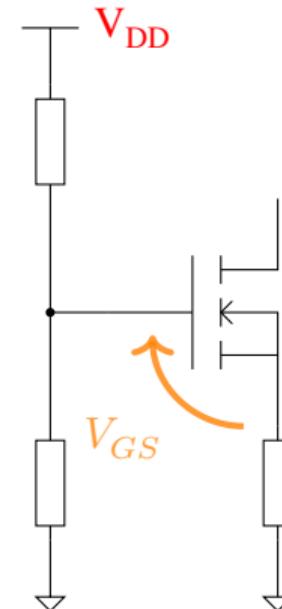

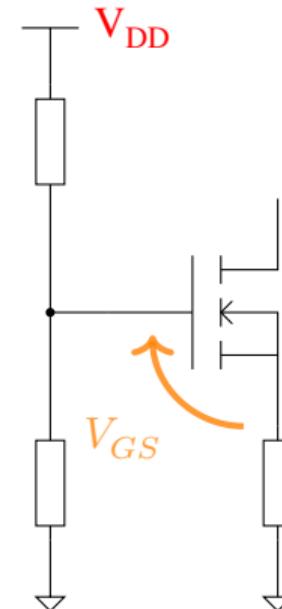

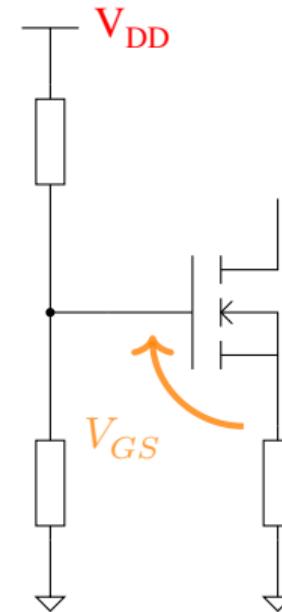

## MOSFET 基本増幅回路のコア

## bipolar 基本増幅回路のコア

## おことわり

ここから話は小信号設計に入りますが、小信号モデルは MOS もバイポーラも一緒なので記号は MOS で行きます。

# 【〇〇接地】とは。

あくまでも小信号視点の呼び方。

ことで作る回路の設計パターン。

# 【〇〇接地】とは。

あくまでも小信号視点の呼び方。

- **小信号の 基準点** (グラウンド、つまり**接地**点) を

ことで作る回路の設計パターン。

# 【〇〇接地】とは。

あくまでも小信号視点の呼び方。

- **小信号の 基準点** (グラウンド、つまり**接地**点) を

- トランジスタの**どこかの端子**、つまり…

ことで作る回路の設計パターン。

# 【〇〇接地】とは。

あくまでも小信号視点の呼び方。

- **小信号の 基準点** (グラウンド、つまり**接地**点) を

- トランジスタの**どこかの端子**、つまり…

- **ソース・ゲート・ドレインのいずれか**にする

ことで作る回路の設計パターン。

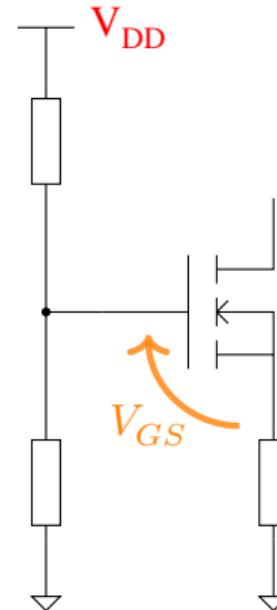

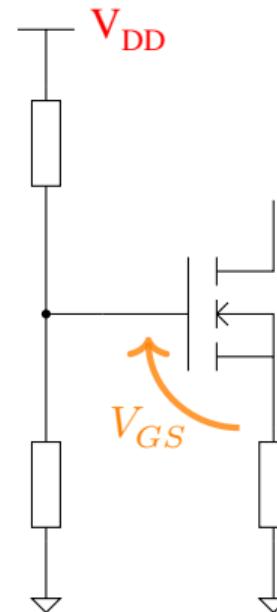

# 【OO接地】其之壹: ソース/エミッタ接地

- ① ソース/エミッタを AC 的に接地する。

や  $v_i$  を変化させる必要がある

ので  $v_i$  に  $v_i$  を

入れる以外選択肢がない。

- ③ すると残った

が出力になる。出力電圧を

出すために負荷抵抗  $R_L$  を入れ

てできあがり。

# 【OO接地】其之壹: ソース/エミッタ接地

- ① ソース/エミッタを AC 的に接地する。

- ②  $V_{GS}$  や を変化させる必要があるので に  $v_i$  を入れる以外選択肢がない。

- ③ すると残った が出力になる。出力電圧を出すために負荷抵抗  $R_L$  を入れてできあがり。

# 【OO接地】其之壹: ソース/エミッタ接地

- ① ソース/エミッタを AC 的に接地する。

- ②  $V_{GS}$  や  $V_{BE}$  を変化させる必要があるので  $v_i$  を入れる以外選択肢がない。

- ③ すると残った

が出力になる。出力電圧を

出すために負荷抵抗  $R_L$  を入れ

てできあがり。

# 【OO接地】其之壹: ソース/エミッタ接地

- ① ソース/エミッタを AC 的に接地する。

- ②  $V_{GS}$  や  $V_{BE}$  を変化させる必要があるので ゲート/ベースに  $v_i$  を入れる以外選択肢がない。

- ③ すると残った

が出力になる。出力電圧を

出すために負荷抵抗  $R_L$  を入れ

てできあがり。

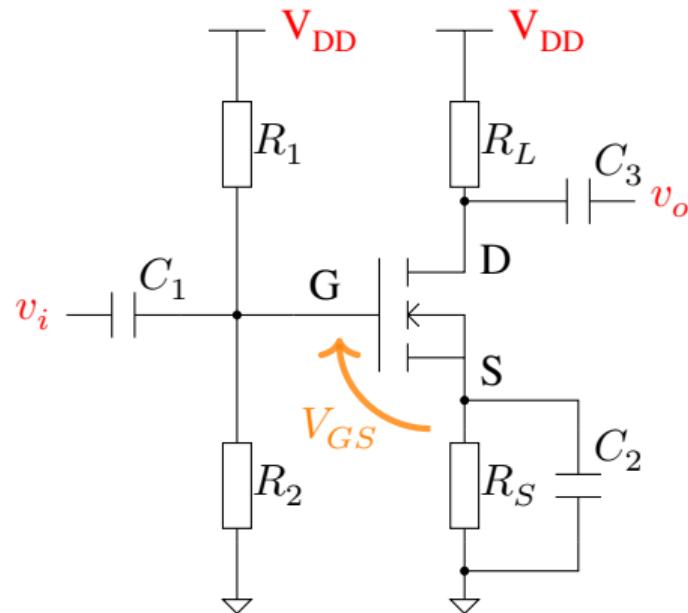

# 【OO接地】其之壹: ソース/エミッタ接地

- ① ソース/エミッタを AC 的に接地する。

- ②  $V_{GS}$  や  $V_{BE}$  を変化させる必要があるので ゲート/ベースに  $v_i$  を入れる以外選択肢がない。

- ③ すると残ったドレイン/コレクタが出力になる。出力電圧を出すために負荷抵抗  $R_L$  を入れてできあがり。

# 【OO接地】其之壹: ソース/エミッタ接地

- ① ソース/エミッタを AC 的に接地する。

- ②  $V_{GS}$  や  $V_{BE}$  を変化させる必要があるので ゲート/ベースに  $v_i$  を入れる以外選択肢がない。

- ③ すると残ったドレイン/コレクタが出力になる。出力電圧を出すために負荷抵抗  $R_L$  を入れてできあがり。

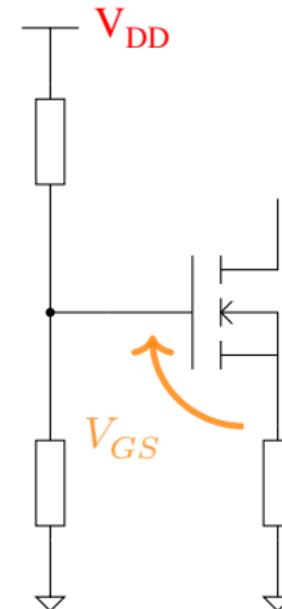

# 【OO接地】其之貳: ゲート/ベース接地

- ① ゲート/ベースを AC 的に接地する。

や  $v_i$  を変化させる必要がある

ので に  $v_i$  を入れる以外選択肢がない。

- ③ すると残った

が出力になる。出力電圧を

出すために負荷抵抗  $R_L$  を入れ

てできあがり。

# 【OO接地】其之貳: ゲート/ベース接地

- ① ゲート/ベースを AC 的に接地する。

- ②  $V_{GS}$  や  $V_{BE}$  を変化させる必要があるので  $v_i$  を入れる以外選択肢がない。

- ③ すると残った  $v_o$  が出力になる。出力電圧を出すために負荷抵抗  $R_L$ を入れてできあがり。

# 【OO接地】其之貳: ゲート/ベース接地

- ① ゲート/ベースを AC 的に接地する。

- ②  $V_{GS}$  や  $V_{BE}$  を変化させる必要があるので  $v_i$  を入れる以外選択肢がない。

- ③ すると残った

が出力になる。出力電圧を

出すために負荷抵抗  $R_L$  を入れ

てできあがり。

# 【OO接地】其之貳: ゲート/ベース接地

- ① ゲート/ベースを AC 的に接地する。

- ②  $V_{GS}$  や  $V_{BE}$  を変化させる必要があるのでソース/エミッタに  $v_i$  を入れる以外選択肢がない。

- ③ すると残った

が出力になる。出力電圧を

出すために負荷抵抗  $R_L$  を入れ

てできあがり。

# 【OO接地】其之貳: ゲート/ベース接地

- ① ゲート/ベースを AC 的に接地する。

- ②  $V_{GS}$  や  $V_{BE}$  を変化させる必要があるのでソース/エミッタに  $v_i$  を入れる以外選択肢がない。

- ③ すると残ったドレイン/コレクタが出力になる。出力電圧を出すために負荷抵抗  $R_L$ を入れてできあがり。

# 【OO接地】其之貳: ゲート/ベース接地

- ① ゲート/ベースを AC 的に接地する。

- ②  $V_{GS}$  や  $V_{BE}$  を変化させる必要があるのでソース/エミッタに  $v_i$  を入れる以外選択肢がない。

- ③ すると残ったドレイン/コレクタが出力になる。出力電圧を出すために負荷抵抗  $R_L$ を入れてできあがり。

前ページのゲート接地増幅回路の小信号における

- ① 電圧利得  $A_v$  を求めよ。

- ② 入力インピーダンス  $Z_i$  を求めよ。

- ③ 出力インピーダンス  $Z_o$  を求めよ。

ただしトランジスタの伝達コンダクタンスを  $g_m$  とする。

ヒント: まずは回路の小信号モデルを書くことから…。

前ページのゲート接地増幅回路の小信号における

- ① 電圧利得  $A_v$  を求めよ。

- ② 入力インピーダンス  $Z_i$  を求めよ。

- ③ 出力インピーダンス  $Z_o$  を求めよ。

ただしトランジスタの伝達コンダクタンスを  $g_m$  とする。

ヒント: まずは回路の小信号モデルを書くことから…。

$$\text{答: } A_v = g_m R_L, Z_i = \frac{R_S}{1+g_m R_S}, Z_o = R_L$$

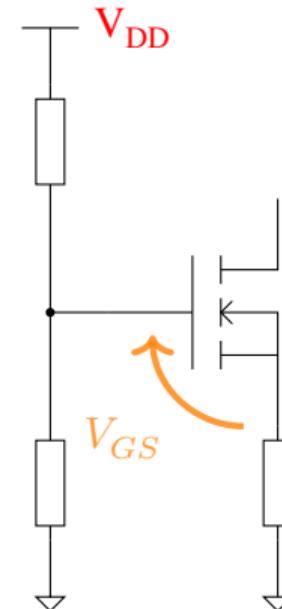

# 【OO接地】其之參: ドレイン/コレクタ接地

- ① ドレイン/コレクタを AC 的に接地…しよう

としたが、邪魔な抵抗器もないのとそのままに直結。(GND じゃダメなのわかる?)

や を変化させる必要がある…ということは、入力は残った2端子ならどっちでも良さそうなものだが、ゲートやベースを出力にするのはいかにも無理な感じがするので **に  $v_i$  を入れること** にする。

- ③ すると残った **が出力** になる。

出力電圧を出すために負荷抵抗  $R_L$  を…入れようと思ったが既にあるのでこれが  $R_L$  だったことにしてできあがり。

# 【OO接地】其之參: ドレイン/コレクタ接地

- ① ドレイン/コレクタを AC 的に接地…しよう

としたが、邪魔な抵抗器もないのとそのまま  $V_{DD}$  や  $V_{CC}$  に直結。(GND じゃダメなのわかる?)

や  $v_i$  を変化させる必要がある…ということは、入力は残った 2 端子ならどっちでも良さそうなものだが、ゲートやベースを出力にするのはいかにも無理な感じがするので **に  $v_i$  を入れること** にする。

- ③ すると残った **が出力** になる。

出力電圧を出すために負荷抵抗  $R_L$  を…入れようと思ったが既にあるのでこれが  $R_L$  だったことにしてできあがり。

# 【OO接地】其之參: ドレイン/コレクタ接地

- ① **ドレイン/コレクタを AC 的に接地**…しよう

としたが、邪魔な抵抗器もないのとそのまま  $V_{DD}$  や  $V_{CC}$  に直結。(GND じゃダメなのわかる?)

- ②  $V_{GS}$  や  $V_{CE}$  を変化させる必要がある…ということは、入力は残った 2 端子ならどっちでも良さそうなものだが、ゲートやベースを出力にするのはいかにも無理な感じがするので **に  $v_i$  を入れる** ことにする。

- ③ すると残った **が出力** になる。

出力電圧を出すために負荷抵抗  $R_L$  を…入れようと思ったが既にあるのでこれが  $R_L$  だったことにしてできあがり。

# 【OO接地】其之參: ドレイン/コレクタ接地

- ① **ドレイン/コレクタを AC 的に接地**…しよう

としたが、邪魔な抵抗器もないのとそのまま  $V_{DD}$  や  $V_{CC}$  に直結。(GND じゃダメなのわかる?)

- ②  $V_{GS}$  や  $V_{BE}$  を変化させる必要がある…ということは、入力は残った 2 端子ならどっちでも良さそうなものだが、ゲートやベースを出力にするのはいかにも無理な感じがするので **に  $v_i$  を入れる** ことにする。

- ③ すると残った **が出力** になる。

出力電圧を出すために負荷抵抗  $R_L$  を…入れようと思ったが既にあるのでこれが  $R_L$  だったことにしてできあがり。

# 【OO接地】其之參: ドレイン/コレクタ接地

- ① **ドレイン/コレクタを AC 的に接地**…しよう

としたが、邪魔な抵抗器もないのとそのまま  $V_{DD}$  や  $V_{CC}$  に直結。(GND じゃダメなのわかる?)

- ②  $V_{GS}$  や  $V_{BE}$  を変化させる必要がある…ということは、入力は残った 2 端子ならどっちでも良さそうなものだが、ゲートやベースを出力にするのはいかにも無理な感じがするので **ゲート/ベースに  $v_i$  を入れること** にする。

- ③ すると残った **が出力** になる。

出力電圧を出すために負荷抵抗  $R_L$  を…入れようと思ったが既にあるのでこれが  $R_L$  だったことにしてできあがり。

# 【OO接地】其之參: ドレイン/コレクタ接地

- ① **ドレイン/コレクタを AC 的に接地**…しよう

としたが、邪魔な抵抗器もないのとそのまま  $V_{DD}$  や  $V_{CC}$  に直結。(GND じゃダメなのわかる?)

- ②  $V_{GS}$  や  $V_{BE}$  を変化させる必要がある…ということは、入力は残った 2 端子ならどっちでも良さそうなものだが、ゲートやベースを出力にするのはいかにも無理な感じがするので **ゲート/ベースに  $v_i$  を入れる** ことにする。

- ③ すると残った**ソース/エミッタが出力** になる。出力電圧を出すために負荷抵抗  $R_L$  を…入れようと思ったが既にあるのでこれが  $R_L$  だったことにしてできあがり。

前ページのドレイン接地増幅回路の小信号における

- ① 電圧利得  $A_v$  を求めよ。

- ② 入力インピーダンス  $Z_i$  を求めよ。

- ③ 出力インピーダンス  $Z_o$  を求めよ。

ただしトランジスタの伝達コンダクタンスを  $g_m$  とする。

ヒント: まずは回路の小信号モデルを書くことから…。

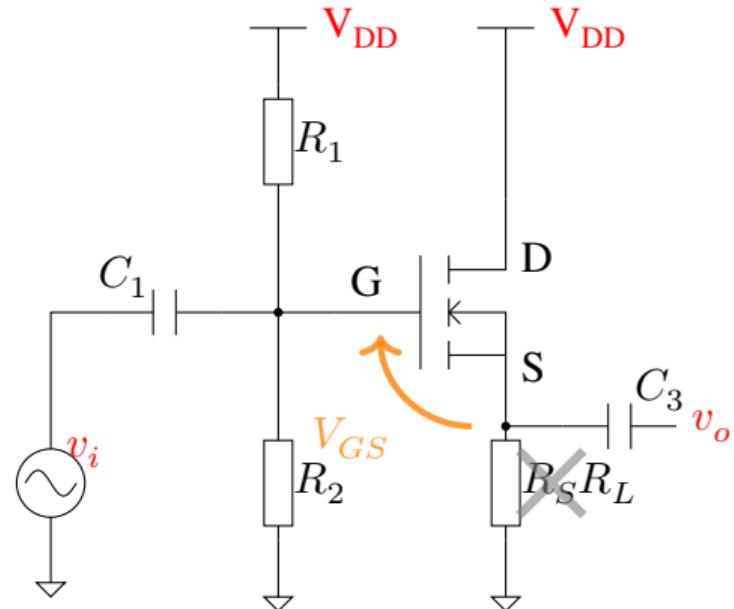

# ドレイン接地増幅回路の練習

前ページのドレイン接地増幅回路の小信号における

- ① 電圧利得  $A_v$  を求めよ。

- ② 入力インピーダンス  $Z_i$  を求めよ。

- ③ 出力インピーダンス  $Z_o$  を求めよ。

ただしトランジスタの伝達コンダクタンスを  $g_m$  とする。

ヒント: まずは回路の小信号モデルを書くことから…。

$$\text{答: } A_v = \frac{g_m R_L}{1 + g_m R_L}, Z_i = R_1 \parallel R_2, Z_o = \frac{R_L}{1 + g_m R_L}$$

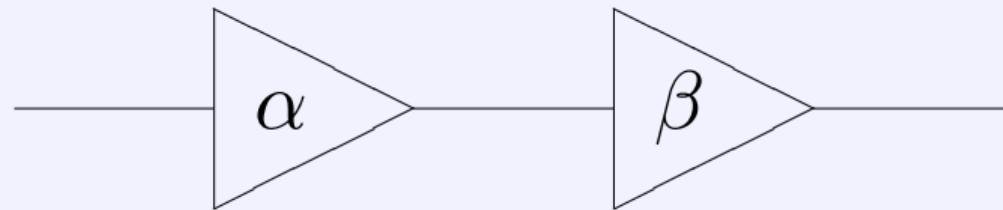

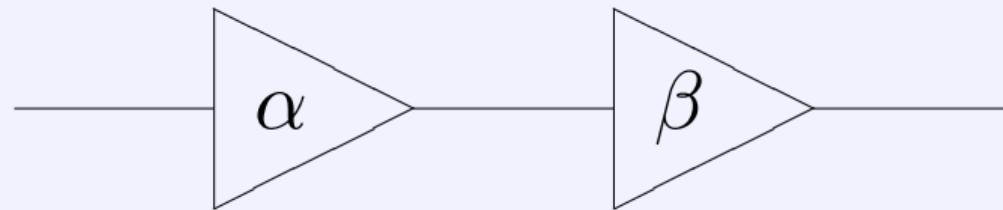

## もんだい

電圧利得が  $\alpha$  の増幅器と  $\beta$  の増幅器があります。縦続接続したら全体の利得はいくつでしょう？

こたえ:

## もんだい

電圧利得が  $\alpha$  の増幅器と  $\beta$  の増幅器があります。縦続接続したら全体の利得はいくつでしょう？

こたえ:  $\alpha\beta$

## もんだい

電圧利得が  $\alpha$  の増幅器と  $\beta$  の増幅器があります。縦続接続したら全体の利得はいくつでしょう？

こたえ:  $\alpha\beta$

で済むならこんなありがたい話はない。

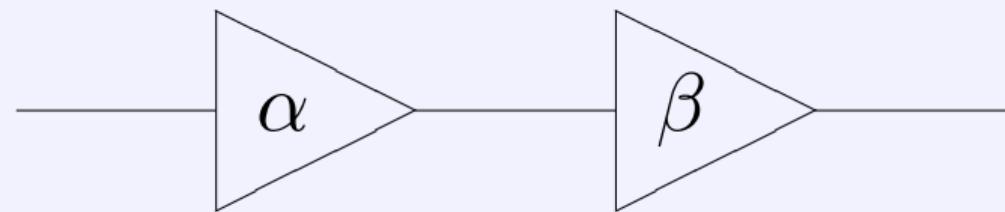

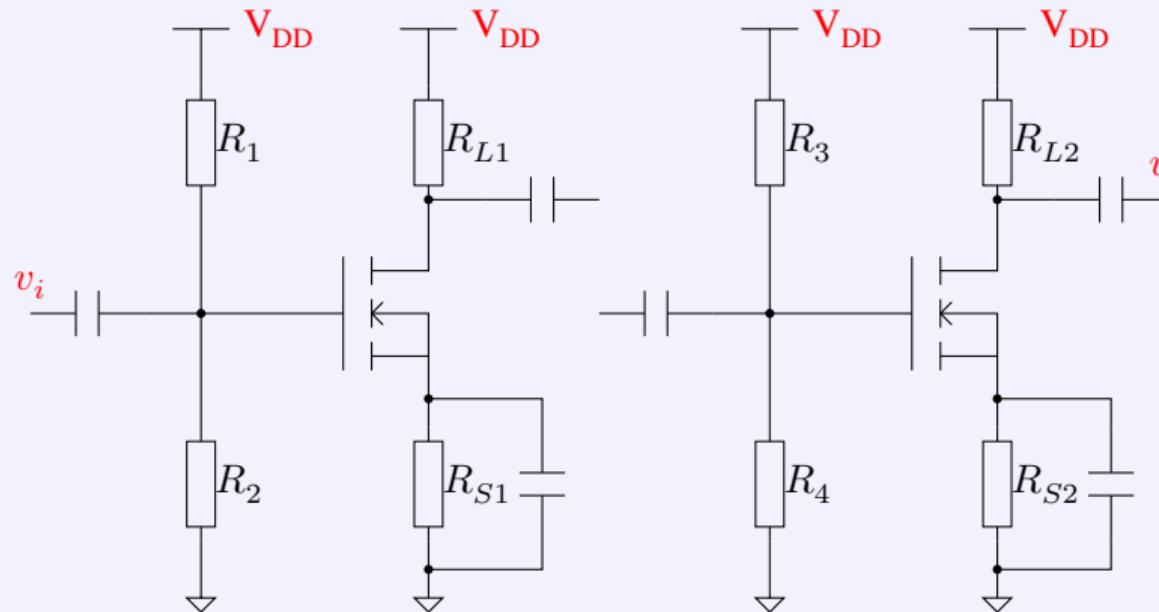

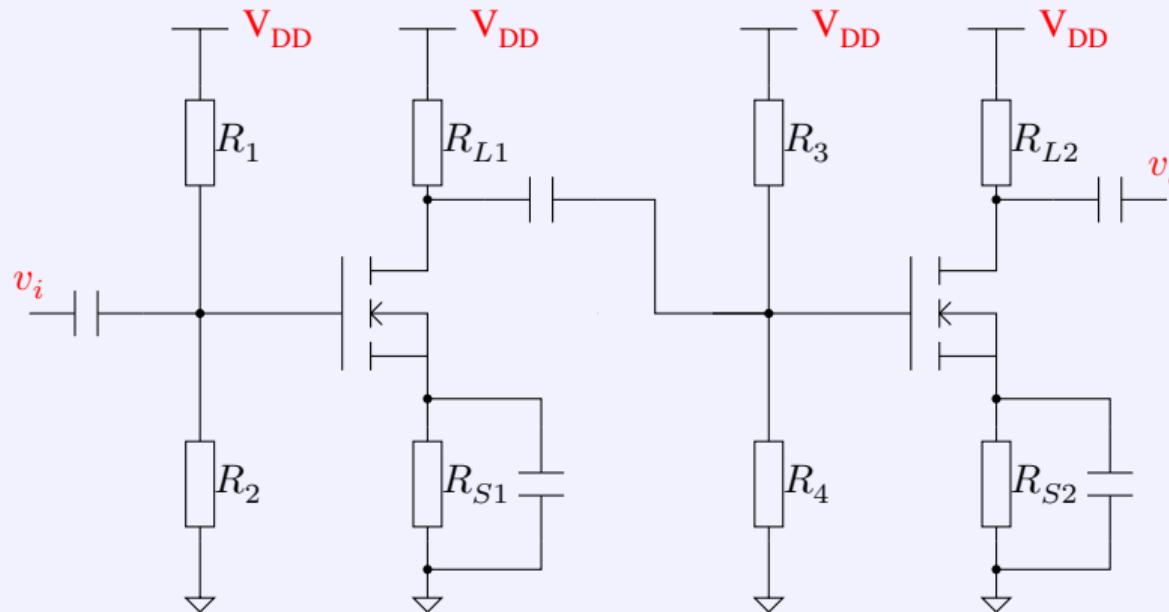

# 縦続接続してみよう

## 基本のソース接地（エミッタ接地）の二段縦続接続

この回路（ごく普通のソース設置増幅回路を縦続接続しただけ）の**小信号モデル**を求めよ。

# 縦続接続してみよう

## 基本のソース接地（エミッタ接地）の二段縦続接続

この回路（ごく普通のソース設置増幅回路を縦続接続しただけ）の **小信号モデル**を求めよ。

$v_i$

$v_o$

モデルが立ったら電圧利得を求めてみよう。

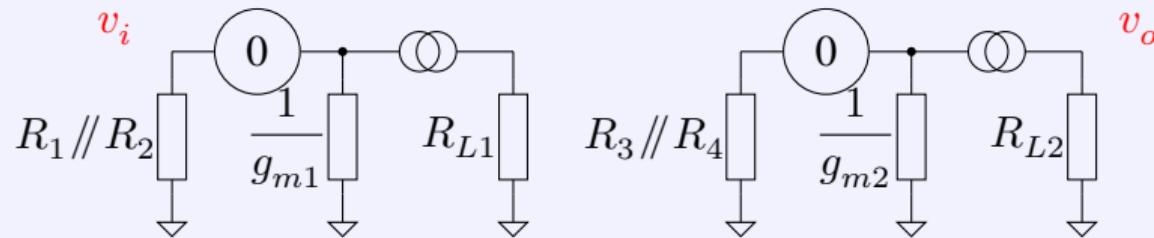

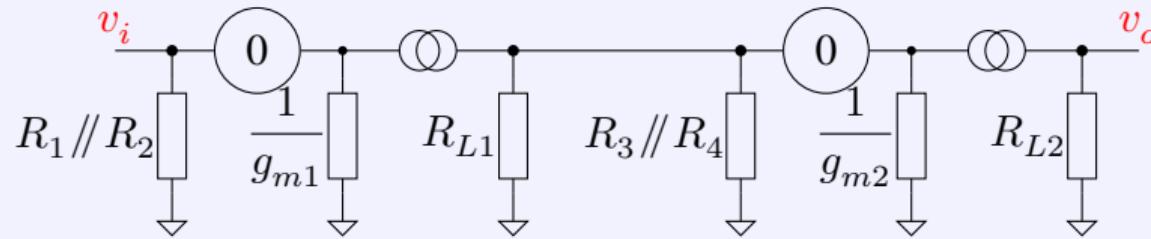

# 縦続接続の小信号モデル

モデルが立ったら電圧利得を求めてみよう。

# 縦続接続の小信号モデル

モデルが立ったら電圧利得を求めてみよう。

# 縦続接続の小信号モデル

モデルが立ったら電圧利得を求めてみよう。

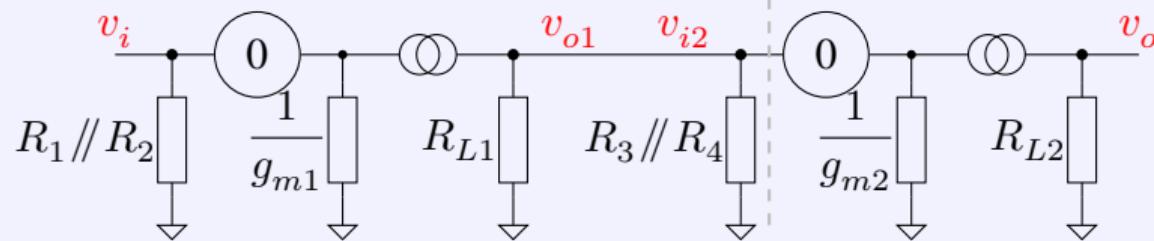

# 継続接続の合成ゲイン

$$v_{o1} =$$

$$v_o =$$

$$A_v = \frac{v_o}{v_i} =$$

# 継続接続の合成ゲイン

$$\begin{aligned}v_{o1} &= -g_{m1}(R_{L1} \parallel R_3 \parallel R_4)v_i = \\v_o &= \end{aligned}$$

$$A_v = \frac{v_o}{v_i} =$$

# 継続接続の合成ゲイン

$$v_{o1} = -g_{m1}(R_{L1} \parallel R_3 \parallel R_4)v_i = v_{i2}$$

$$v_o =$$

$$A_v = \frac{v_o}{v_i} =$$

$$\begin{aligned}v_{o1} &= -g_{m1}(R_{L1} \parallel R_3 \parallel R_4)v_i = v_{i2} \\v_o &= -g_{m2} R_{L2} v_{i2}\end{aligned}$$

$$A_v = \frac{v_o}{v_i} =$$

# 縦続接続の合成ゲイン

$$\begin{aligned}v_{o1} &= -g_{m1}(R_{L1} \parallel R_3 \parallel R_4)v_i = v_{i2} \\v_o &= -g_{m2} R_{L2} v_{i2} \\&= g_{m1} g_{m2} R_{L2} (R_{L1} \parallel R_3 \parallel R_4)v_i\end{aligned}$$

$$A_v = \frac{v_o}{v_i} =$$

$$\begin{aligned}v_{o1} &= -g_{m1}(R_{L1} \parallel R_3 \parallel R_4)v_i = v_{i2} \\v_o &= -g_{m2} R_{L2} v_{i2} \\&= g_{m1} g_{m2} R_{L2} (R_{L1} \parallel R_3 \parallel R_4)v_i\end{aligned}$$

$$A_v = \frac{v_o}{v_i} = g_{m1} g_{m2} R_{L2} (R_{L1} \parallel R_3 \parallel R_4)$$

$$A_v = \frac{v_o}{v_i} = g_{m1} g_{m2} R_{L2} (\textcolor{red}{R_{L1} // R_3 // R_4})$$

- 単純な積だったらのはず。これよりもゲインはなっている。

- もしが大きければゲインの低下は小さくて済む。そんなわけでは大きいほうが良い、とされる（ことが多い）。

- うまくバイアスを設定してやって  $R_3, R_4 = \infty$  にするのも良い。

$$A_v = \frac{v_o}{v_i} = g_{m1} g_{m2} R_{L2} (R_{L1} \parallel R_3 \parallel R_4)$$

- 単純な積だったら  $g_{m1} g_{m2} R_{L2} R_{L1}$  のはず。これよりもゲインはなっている。

- もしが大きければゲインの低下は小さくて済む。そんなわけでは大きいほうが良い、とされる(ことが多い)。

- うまくバイアスを設定してやって  $R_3, R_4 = \infty$  にするのも良い。

$$A_v = \frac{v_o}{v_i} = g_{m1} g_{m2} R_{L2} (R_{L1} \parallel R_3 \parallel R_4)$$

- 単純な積だったら  $g_{m1} g_{m2} R_{L2} R_{L1}$  のはず。これよりもゲインは小さくなっている。

- もし が大きければゲインの低下は小さくて済む。そんなわけで は大きいほうが良い、とされる（ことが多い）。

- うまくバイアスを設定してやって  $R_3, R_4 = \infty$  にするのも良い。

$$A_v = \frac{v_o}{v_i} = g_{m1} g_{m2} R_{L2} (R_{L1} \parallel R_3 \parallel R_4)$$

- 単純な積だったら  $g_{m1} g_{m2} R_{L2} R_{L1}$  のはず。これよりもゲインは小さくなっている。

- もし  $R_3 \parallel R_4$  が大きければゲインの低下は小さくて済む。そんなわけで は大きいほうが良い、とされる(ことが多い)。

- うまくバイアスを設定してやって  $R_3, R_4 = \infty$  にするのも良い。

$$A_v = \frac{v_o}{v_i} = g_{m1} g_{m2} R_{L2} (R_{L1} \parallel R_3 \parallel R_4)$$

- 単純な積だったら  $g_{m1} g_{m2} R_{L2} R_{L1}$  のはず。これよりもゲインは小さくなっている。

- もし  $R_3 \parallel R_4$  が大きければゲインの低下は小さくて済む。そんなわけで **入力インピーダンス** は大きいほうが良い、とされる（ことが多い）。

- うまくバイアスを設定してやって  $R_3, R_4 = \infty$  にするのも良い。

# ミニレポート課題 (受付期間: 授業当日～次回授業の前日)

受付期間外には提出しないこと。(自動処理しています。)

『ゲート接地増幅回路の練習』を解け。答えのみではなく、**きちんととした説明をつけること**。以下の語をそれぞれ一度以上使うこと。

ゲート, ソース, ドレイン, 接地, キャパシタ, 負荷

提出は下記 URL の Google Forms。歪んでいない、開いた時に横倒しになっていない、コントラストが読むに耐えうる **PDF で提出すること**。**手書きを写真撮影する場合はスキャナもしくはスキャナアプリの使用を必須とする。**

<https://forms.gle/MpUmErDi6qk8GSUC6>